## CMSC 313 COMPUTER ORGANIZATION & ASSEMBLY LANGUAGE PROGRAMMING

**LECTURE 24, SPRING 2013**

### **TOPICS TODAY**

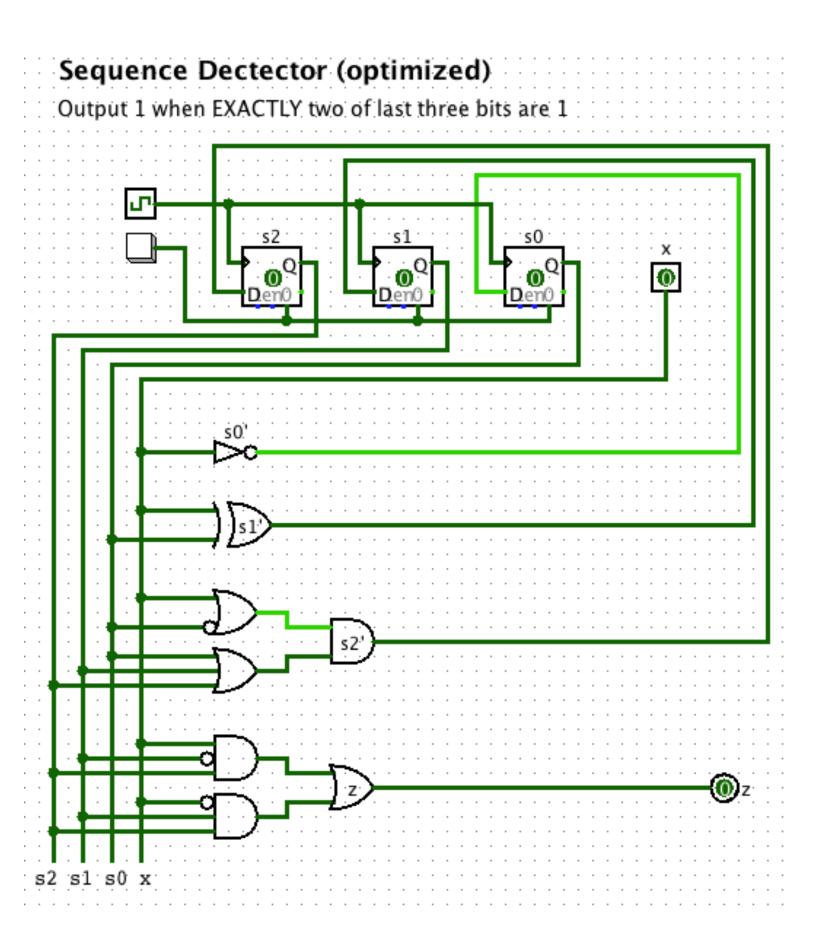

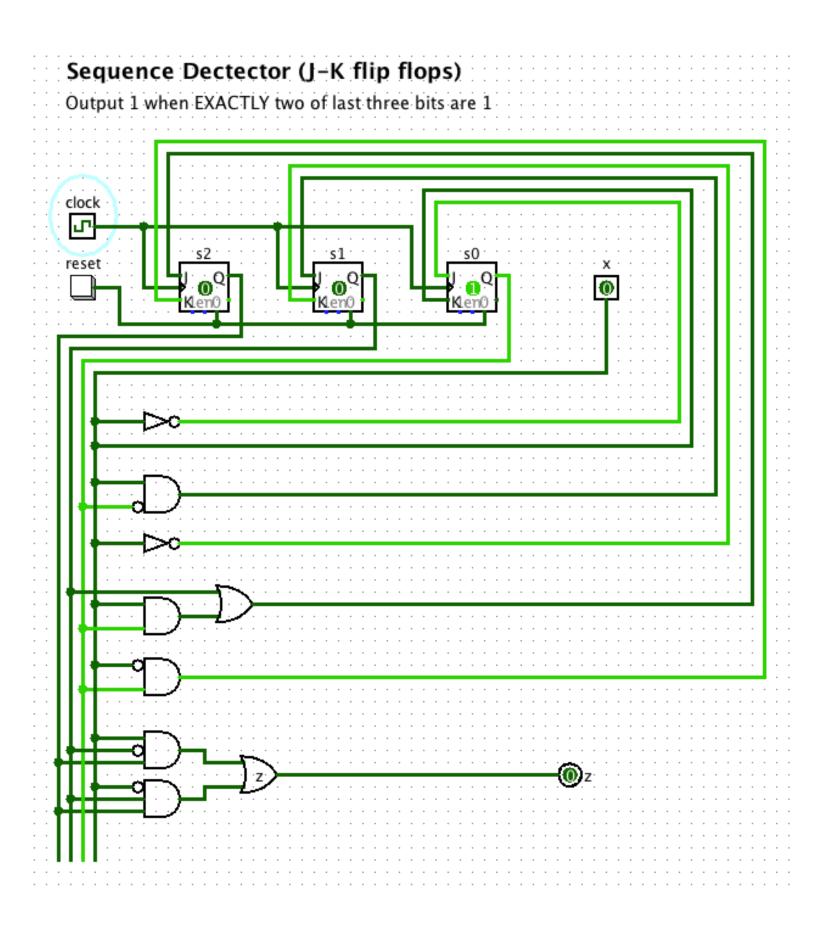

- Example: Sequence Detector

- Finite State Machine Simplification

- Circuit Minimization

- State Reduction

- State Assignment

- Choice of Flip Flop (not covered)

# EXAMPLE: SEQUENCE DETECTOR

### **Example: A Sequence Detector**

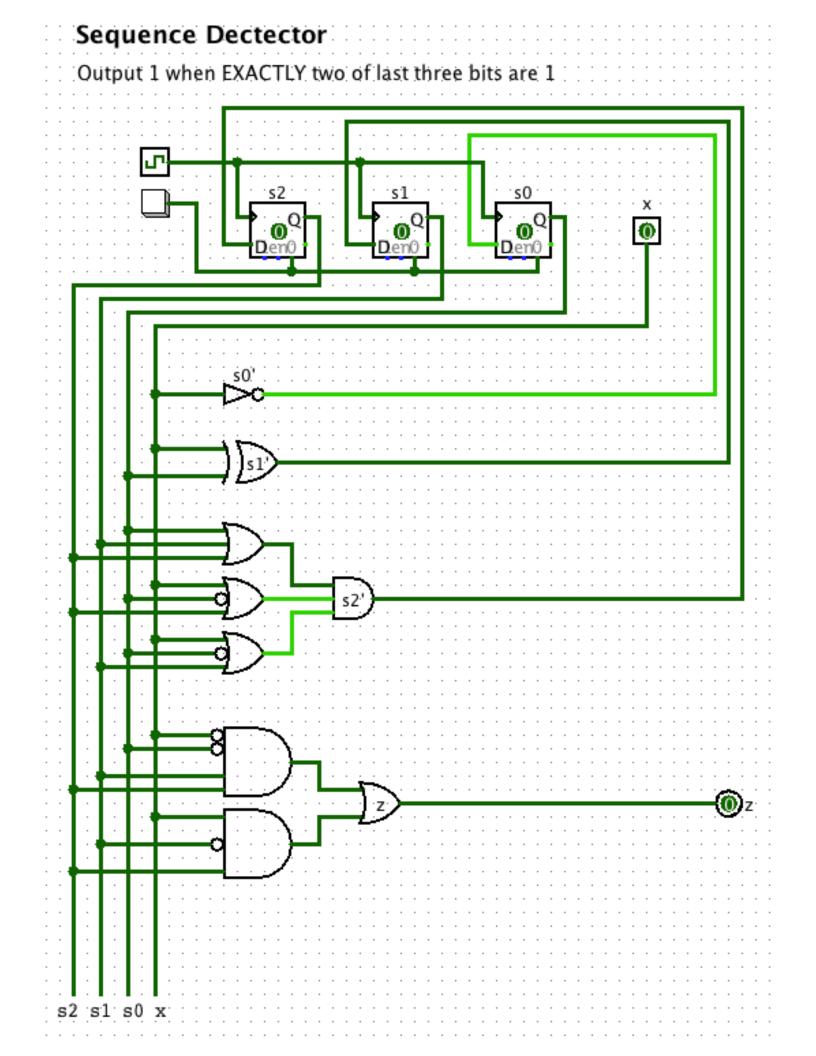

- <u>Example</u>: Design a machine that outputs a 1 when exactly two of the last three inputs are 1.

- e.g. input sequence of 011011100 produces an output sequence of 001111010.

- Assume input is a 1-bit serial line.

- Use D flip-flops and 8-to-1 Multiplexers.

- Start by constructing a state transition diagram (next slide).

Principles of Computer Architecture by M. Murdocca and V. Heuring

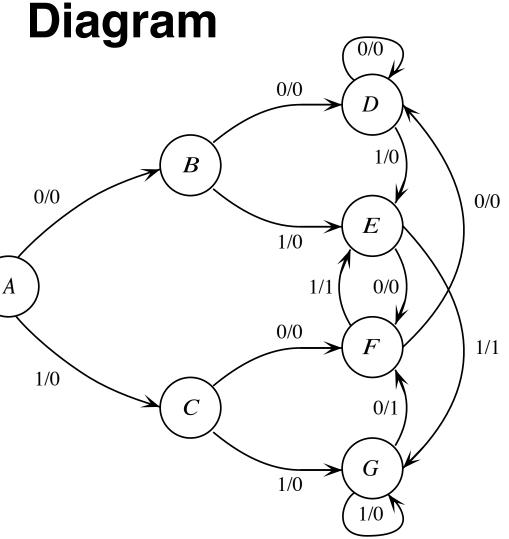

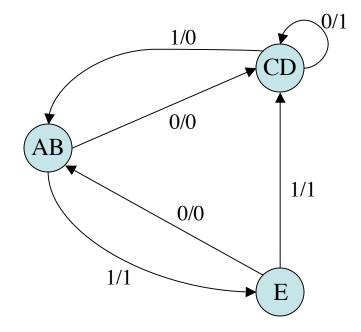

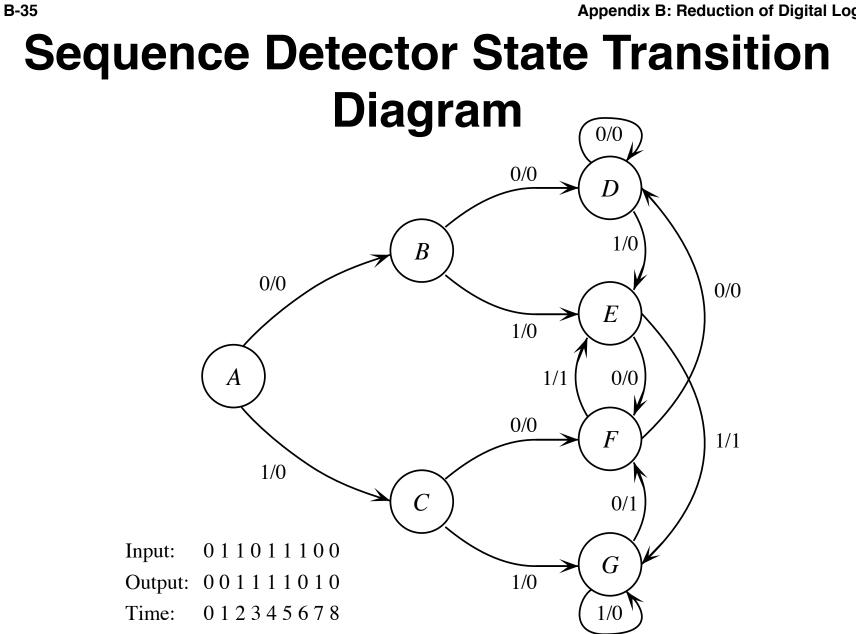

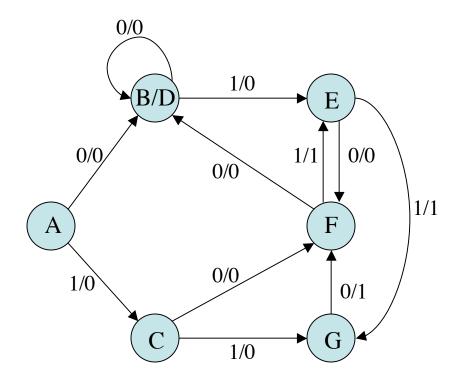

#### Sequence Detector State Transition Diagram

Design a machine that outputs a 1 when exactly two of the last three inputs are 1.

Principles of Computer Architecture by M. Murdocca and V. Heuring

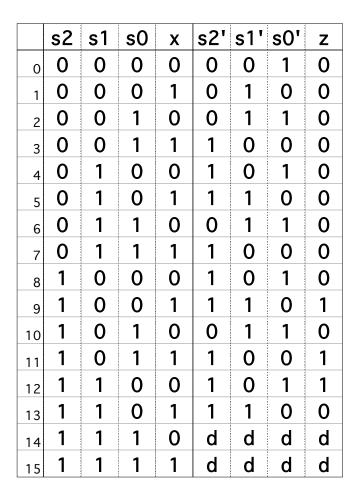

#### **Sequence Detector State Table**

| Input         | X                       |  |  |

|---------------|-------------------------|--|--|

| Present state | 0 1                     |  |  |

| A             | <i>B</i> /0 <i>C</i> /0 |  |  |

| В             | <i>D</i> /0 <i>E</i> /0 |  |  |

| С             | <i>F</i> /0 <i>G</i> /0 |  |  |

| D             | <i>D</i> /0 <i>E</i> /0 |  |  |

| E             | <i>F</i> /0 <i>G</i> /1 |  |  |

| F             | <i>D</i> /0 <i>E</i> /1 |  |  |

| G             | <i>F</i> /1 <i>G</i> /0 |  |  |

Principles of Computer Architecture by M. Murdocca and V. Heuring

#### **Sequence Detector State Assignment**

| Input                                                | X                                                                               |  |  |

|------------------------------------------------------|---------------------------------------------------------------------------------|--|--|

| Present state                                        | 0 1                                                                             |  |  |

| $A: \begin{array}{c} S_2 S_1 S_0 \\ 000 \end{array}$ | $\begin{array}{ccc} s_2 s_1 s_0 z & s_2 s_1 s_0 z \\ 001/0 & 010/0 \end{array}$ |  |  |

| <i>B</i> : 001                                       | 011/0 100/0                                                                     |  |  |

| <i>C</i> : 010                                       | 101/0 110/0                                                                     |  |  |

| D: 011                                               | 011/0 100/0                                                                     |  |  |

| <i>E</i> : 100                                       | 101/0 110/1                                                                     |  |  |

| <i>F</i> : 101                                       | 011/0 100/1                                                                     |  |  |

| <i>G</i> : 110                                       | 101/1 110/0                                                                     |  |  |

(a)

| Input and | Next state       |

|-----------|------------------|

| state at  | and output at    |

| time t    | time <i>t</i> +1 |

| <i>s</i> <sub>2</sub> | <i>s</i> <sub>1</sub> | <i>s</i> <sub>0</sub> | x | $s_2 s_1 s_0 z$ |

|-----------------------|-----------------------|-----------------------|---|-----------------|

| 0                     | 0                     | 0                     | 0 | 0010            |

| 0                     | 0                     | 0                     | 1 | 0 1 0 0         |

| 0                     | 0                     | 1                     | 0 | 0 1 1 0         |

| 0                     | 0                     | 1                     | 1 | $1 \ 0 \ 0 \ 0$ |

| 0                     | 1                     | 0                     | 0 | 1 0 1 0         |

| 0                     | 1                     | 0                     | 1 | 1 1 0 0         |

| 0                     | 1                     | 1                     | 0 | 0 1 1 0         |

| 0                     | 1                     | 1                     | 1 | 1000            |

| 1                     | 0                     | 0                     | 0 | 1010            |

| 1                     | 0                     | 0                     | 1 | 1 1 0 1         |

| 1                     | 0                     | 1                     | 0 | 0 1 1 0         |

| 1                     | 0                     | 1                     | 1 | 1 0 0 1         |

| 1                     | 1                     | 0                     | 0 | 1 0 1 1         |

| 1                     | 1                     | 0                     | 1 | 1 1 0 0         |

| 1                     | 1                     | 1                     | 0 | d d d d         |

| 1                     | 1                     | 1                     | 1 | d d d d         |

|                       |                       |                       |   |                 |

(b)

Principles of Computer Architecture by M. Murdocca and V. Heuring

# FINITE STATE MACHINE SIMPLIFICATION

# **CIRCUIT MINIMIZATION**

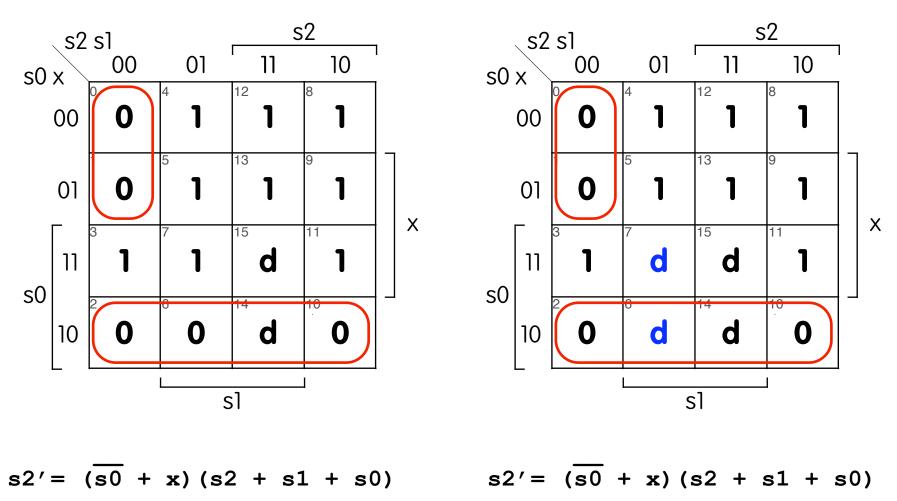

$s2' = (\overline{s0} + x)(s2 + s1 + s0)$

$s1' = \overline{s0} x + s0 \overline{x} = s0 x r x$

$$s0' = \overline{x}$$

$$z = s2 \overline{s1} x + s2 s1 \overline{x}$$

#### **Notes on K-maps**

- Also works for POS

- Takes 2<sup>n</sup> time for formulas with n variables

- Only optimizes two-level logic

- $\diamond$  Reduces number of terms, then number of literals in each term

- Assumes inverters are free

- Does not consider minimizations across functions

- Circuit minimization is generally a hard problem

- Quine-McCluskey can be used with more variables

- CAD tools are available if you are serious

## Karnaugh Maps

- Implicant: rectangle with 1, 2, 4, 8, 16 ... 1's

- Prime Implicant: an implicant that cannot be extended into a larger implicant

- Essential Prime Implicant: the only prime implicant that covers some 1

- K-map Algorithm (not from M&H):

1. Find ALL the prime implicants. Be sure to check every 1 and to use don't cares.

2. Include all essential prime implicants.

3. Try all possibilities to find the minimum cover for the remaining 1's.

### **CIRCUIT MINIMIZATION IS HARD**

- Unix systems store passwords in encrypted form.

- User types x, system computes f(x) and looks for f(x) in a file

- Suppose we use 64-bit passwords and I want to find the password x such that f(x) = y.

- Let  $g_i(x) = 0$  if f(x) = y and the i<sup>th</sup> bit of x is 0. 1 otherwise

- If the i<sup>th</sup> bit of x is 1, then g<sub>i</sub>(x) outputs 1 for every x and g<sub>i</sub>(x) has a very, very simple circuit.

- If you can simplify every circuit quickly, then you can crack passwords quickly.

# Simplifying Finite State Machines

- State Reduction: equivalent FSM with fewer states

- State Assignment: choose an assignment of bit patterns to states (e.g., A is 010) that results in a smaller circuit

- Choice of flip-flops: use D flip-flops, J-K flip-flops or a T flip-flops? a good choice could lead to simpler circuits.

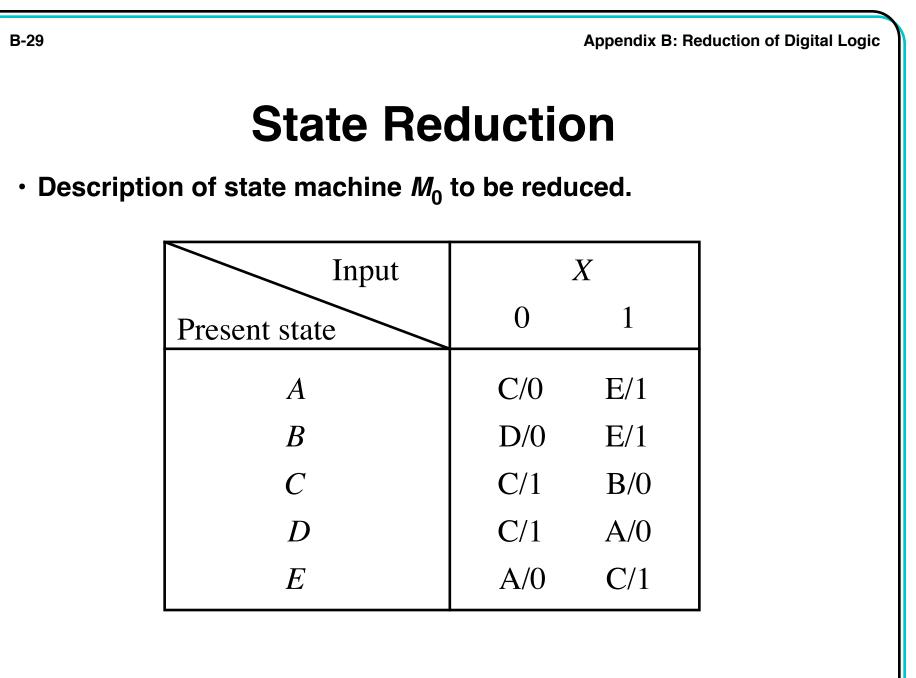

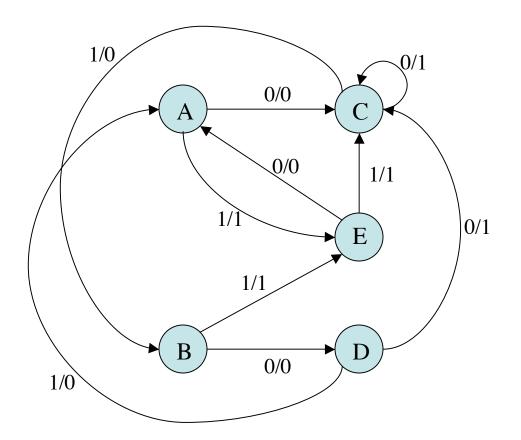

# **STATE REDUCTION**

Principles of Computer Architecture by M. Murdocca and V. Heuring

State Reduction Example: original transition diagram

# **State Reduction Algorithm**

1. Use a 2-dimensional table — an entry for each pair of states.

2. Two states are "distinguished" if:

a. States X and Y of a finite state machine M are distinguished if there exists an input r such that the output of M in state X reading input r is different from the output of M in state Y reading input r.

b. States X and Y of a finite state machine are distinguished if there exists an input r such that M in state X reading input r goes to state X', M in state Y reading input r goes to state Y' and we already know that X' and Y' are distinguished states.

- 3. For each pair (X,Y), check if X and Y are distinguished using the definition above.

- 4. At the end of the algorithm, states that are not found to be distinguished are in fact equivalent.

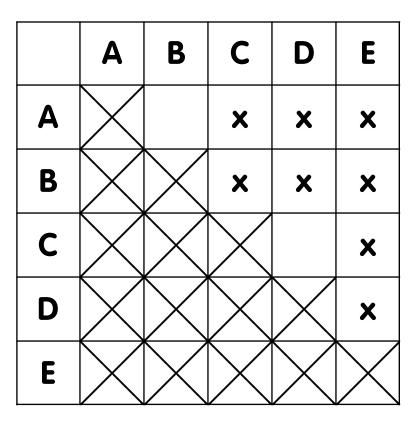

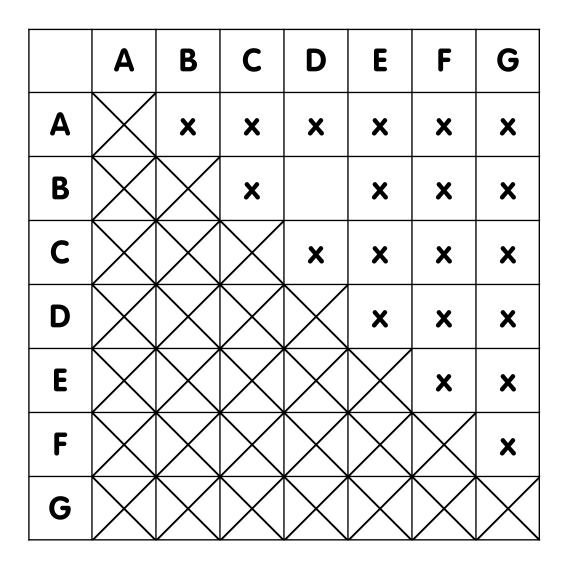

#### **State Reduction Table**

- An x entry indicates that the pair of states are known to be distinguished.

- A & B are equivalent, C & D are equivalent

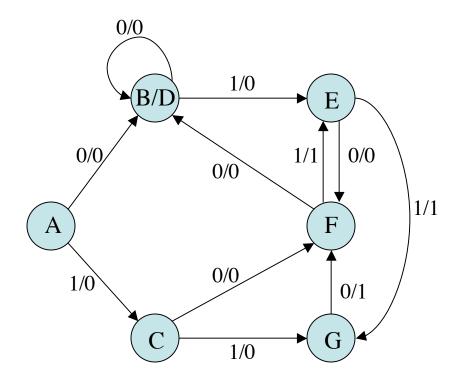

#### State Reduction Example: reduced transition diagram

UMBC, CMSC 313, Richard Chang <chang@umbc.edu>

# **State Reduction Algorithm Performance**

- As stated, the algorithm takes O(n<sup>4</sup>) time for a FSM with n states, because each pass takes O(n<sup>2</sup>) time and we make at most O(n<sup>2</sup>) passes.

- A more clever implementation takes O(n<sup>2</sup>) time.

- The algorithm produces a FSM with the fewest number states possible.

- Performance and correctness can be proven.

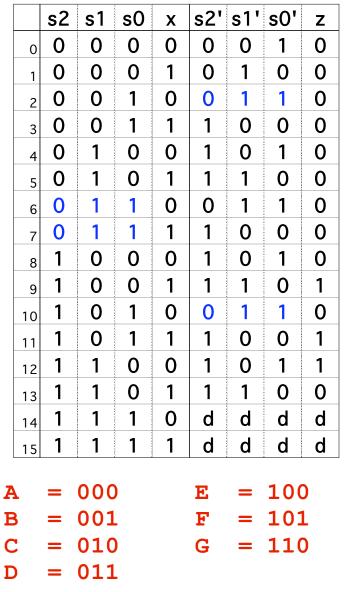

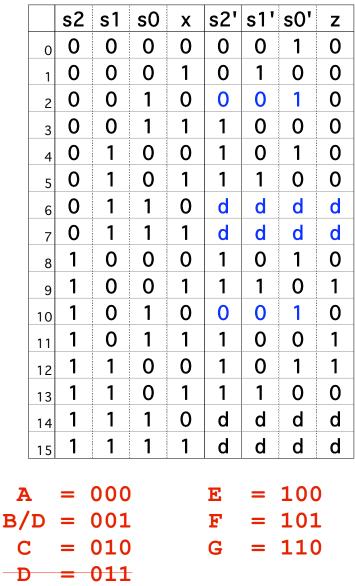

# **STATE ASSIGNMENT**

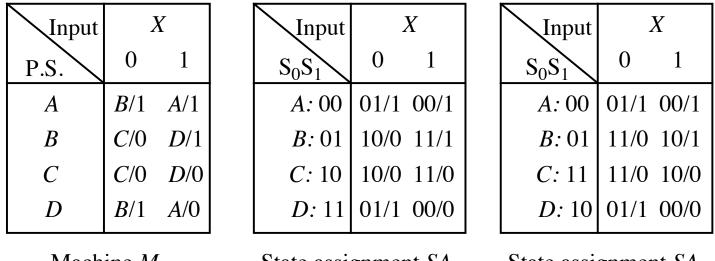

#### **The State Assignment Problem**

• Two state assignments for machine  $M_2$ .

Machine  $M_2$

State assignment  $SA_0$

State assignment  $SA_1$

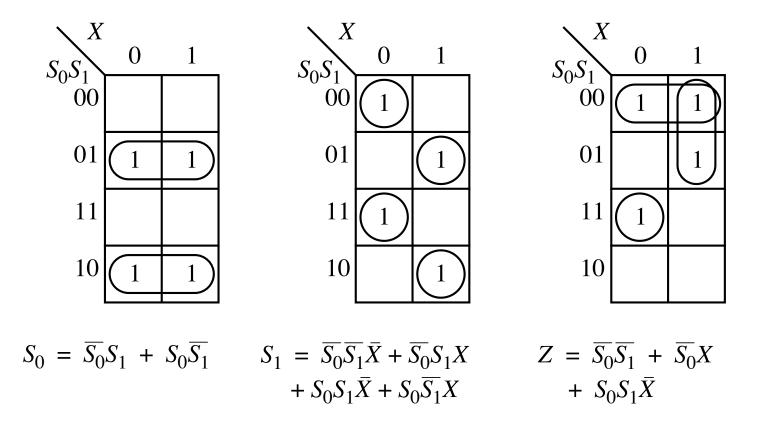

• Boolean equations for machine  $M_2$  using state assignment SA<sub>0</sub>.

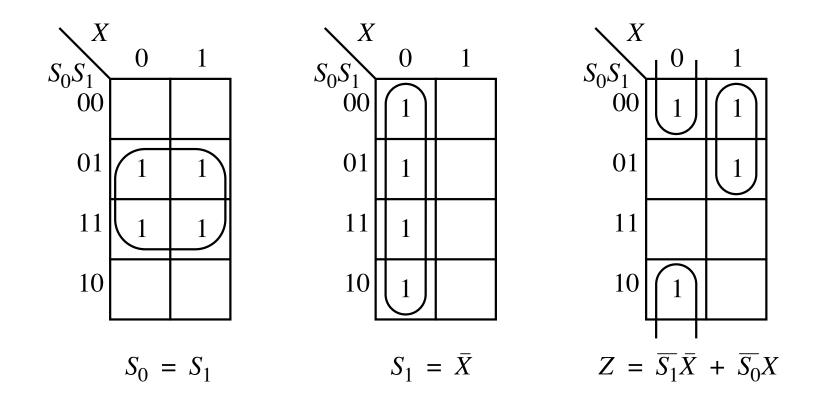

#### State Assignment SA<sub>1</sub>

• Boolean equations for machine  $M_2$  using state assignment SA<sub>1</sub>.

# **State Assignment Heuristics**

#### • No known efficient alg. for best state assignment

#### • Some heuristics (rules of thumb):

- $\diamond$  The initial state should be simple to reset all zeroes or all ones.

- Minimize the number of state variables that change on each transition.

- Maximize the number of state variables that don't change on each transition.

- Second Second

- If there are unused states (when the number of states s is not a power of 2), choose the unused state variable combinations carefully. (Don't just use the first s combination of state variables.)

- Decompose the set of state variables into bits or fields that have well-defined meaning with respect to the input or output behavior.

- Consider using more than the minimum number of states to achieve the objectives above.

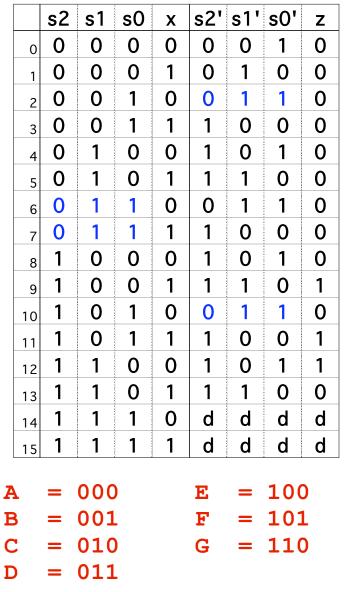

# APPLY STATE REDUCTION & STATE ASSIGNMENT TO SEQUENCE DETECTOR

**Appendix B: Reduction of Digital Logic**

Principles of Computer Architecture by M. Murdocca and V. Heuring

#### **Sequence Detector State Table**

| Input         | X                       |  |  |

|---------------|-------------------------|--|--|

| Present state | 0 1                     |  |  |

| A             | <i>B</i> /0 <i>C</i> /0 |  |  |

| В             | <i>D</i> /0 <i>E</i> /0 |  |  |

| C             | <i>F</i> /0 <i>G</i> /0 |  |  |

| D             | <i>D</i> /0 <i>E</i> /0 |  |  |

| E             | <i>F</i> /0 <i>G</i> /1 |  |  |

| F             | <i>D</i> /0 <i>E</i> /1 |  |  |

| G             | <i>F</i> /1 <i>G</i> /0 |  |  |

Principles of Computer Architecture by M. Murdocca and V. Heuring

#### **Sequence Detector State Reduction Table**

#### Sequence Detector Reduced State Table

| Input           | X      |            |  |

|-----------------|--------|------------|--|

| Present state   | 0      | l          |  |

| A:A'            |        | '/0        |  |

| BD: B'<br>C: C' |        | '/0<br>'/0 |  |

| E:D'            | E'/0 F | /1         |  |

| F: E'<br>G: F'  |        | '/1<br>'/0 |  |

Principles of Computer Architecture by M. Murdocca and V. Heuring

### **Sequence Detector State Assignment**

| X                         |

|---------------------------|

| 0 1                       |

| $S_2S_1S_0Z$ $S_2S_1S_0Z$ |

| 001/0 010/0               |

| 001/0 011/0               |

| 100/0 101/0               |

| 100/0 101/1               |

| 001/0 011/1               |

| 100/1 101/0               |

|                           |

Principles of Computer Architecture by M. Murdocca and V. Heuring

Appendix B: Reduction of Digital Logic

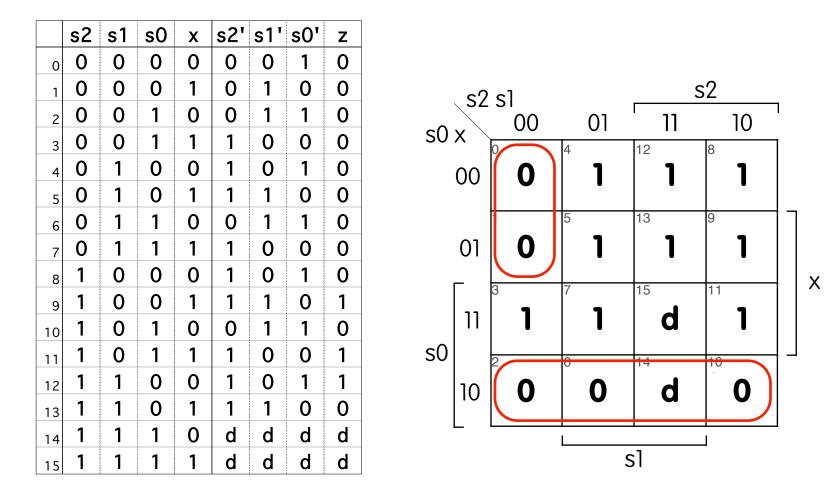

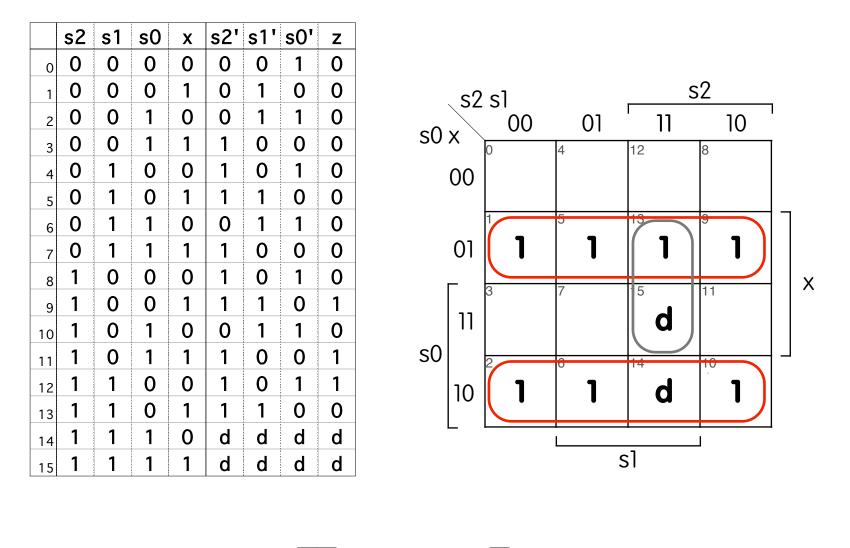

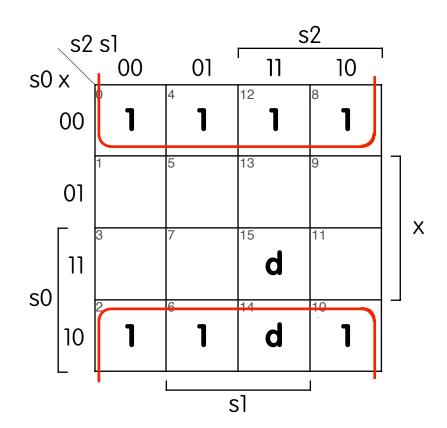

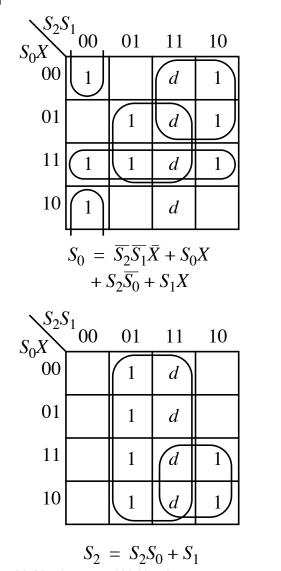

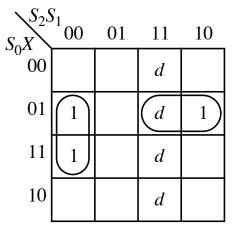

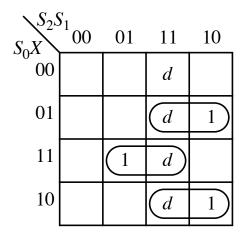

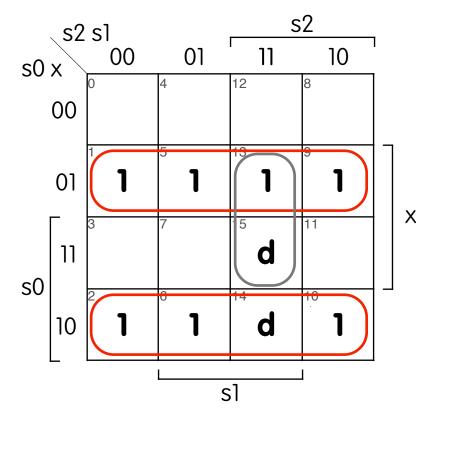

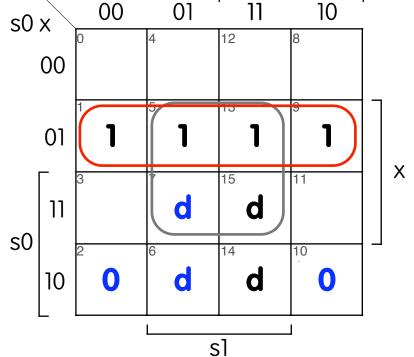

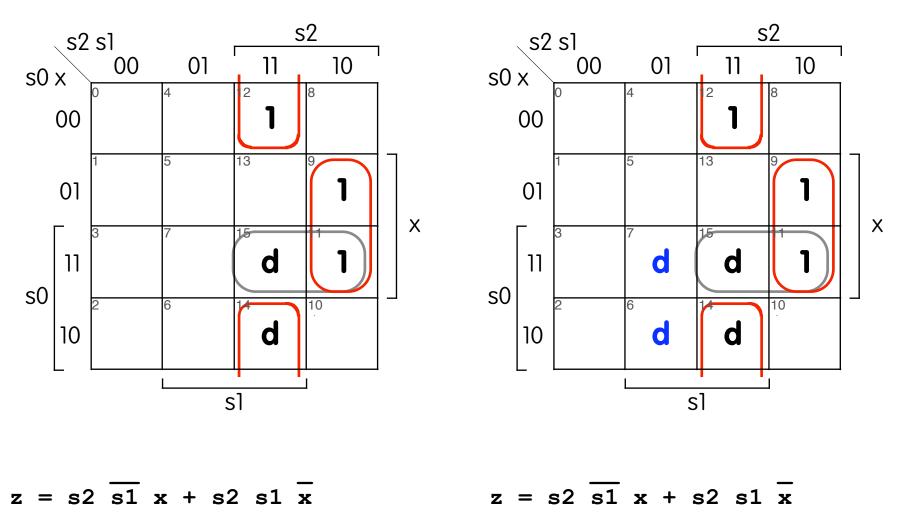

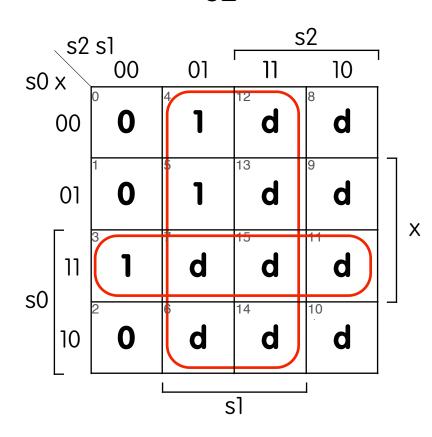

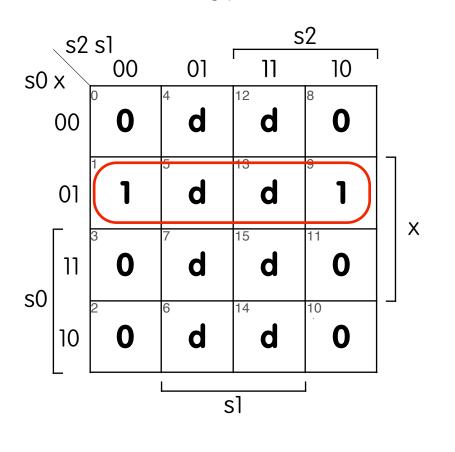

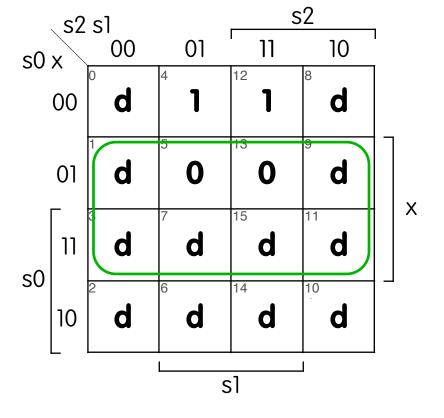

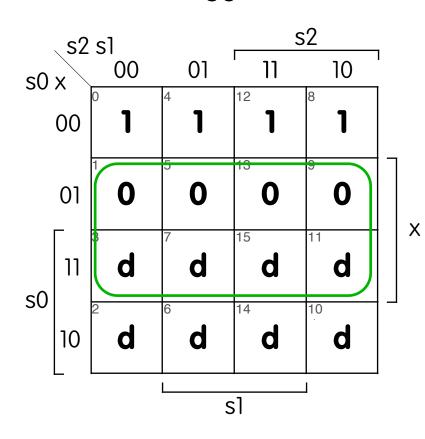

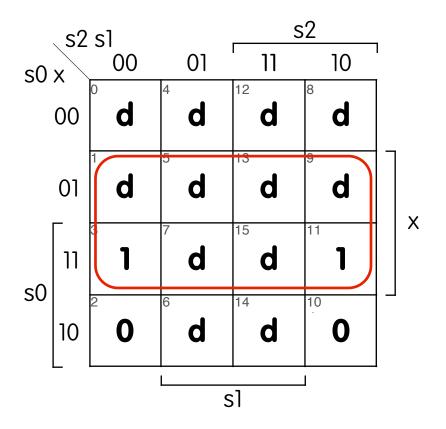

### **Sequence Detector K-Maps**

K-map reduction of next state and output functions for sequence detector.

Principles of Computer Architecture by M. Murdocca and V. Heuring

$S_1 = \overline{S_2}\overline{S_1}X + S_2\overline{S_0}X$

$Z = S_2 \overline{S_0} X + S_1 S_0 X + S_2 S_0 \overline{X}$

© 1999 M. Murdocca and V. Heuring

B-40

### **Improved Sequence Detector?**

#### • Formulas from the 7-state FSM:

$$s2' = (\overline{s0} + x) (s2 + s1 + s0)$$

$$s1' = \overline{s0} x + s0 \overline{x} = s0 \text{ xor } x$$

$$s0' = \overline{x}$$

$$z = s2 \overline{s1} x + s2 \overline{s1} \overline{x}$$

#### • Formulas from the 6-state FSM:

$$s2' = s2 s0 + s1$$

$$s1' = \overline{s2} \overline{s1} x + s2 \overline{s0} x$$

$$s0' = \overline{s2} \overline{s1} \overline{x} + s0 x + s2 \overline{s0} + s1 x$$

$$z = s2 \overline{s0} x + s1 s0 x + s2 s0 \overline{x}$$

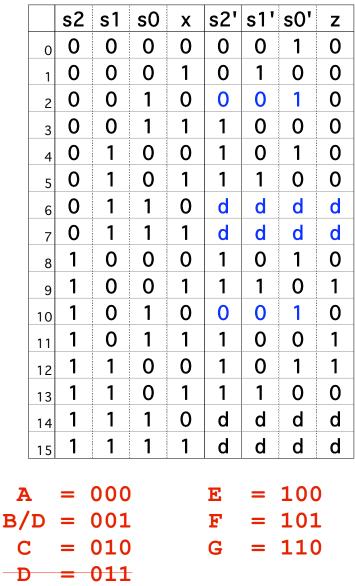

# **Sequence Detector State Assignment**

#### 7-state

#### new 6-state

7-state

new 6-state

7-state

new 6-state

Г

s2

$s1' = \overline{s0} x + s0 \overline{x}$

$s1' = \overline{s0} x$

s2 s1

7-state

new 6-state

s2

s0' = x

s0' = x

7-state

new 6-state

### **Improved Sequence Detector**

#### • Textbook formulas for the 6-state FSM:

$$s2' = s2 s0 + s1$$

$$s1' = \overline{s2} \overline{s1} x + s2 \overline{s0} x$$

$$s0' = \overline{s2} \overline{s1} \overline{x} + s0 x + s2 \overline{s0} + s1 x$$

$$z = s2 \overline{s0} x + s1 s0 x + s2 s0 \overline{x}$$

#### • New formulas for the 6-state FSM:

$$s2' = (\overline{s0} + x) (s2 + s1 + s0)$$

$$s1' = \overline{s0} x$$

$$s0' = \overline{x}$$

$$z = s2 \overline{s1} x + s2 \overline{s1} \overline{x}$$

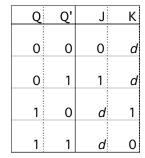

# CHOICE OF FLIP FLOP (NOT COVERED)

D

flip-flop

#### **Excitation Tables**

• Each table shows the settings that must be applied at the inputs at time t in order to change the outputs at time *t*+1.

|                  | $Q_t$ | $Q_{t+1}$ | S                                     | R      |

|------------------|-------|-----------|---------------------------------------|--------|

| S-R              | 0     | 0         | 0                                     | 0      |

| flip-flop        | 0     | 1         | 1                                     | 0      |

|                  | 1     | 0         | 0                                     | 1      |

|                  | 1     | 1         | 0                                     | 0      |

|                  |       |           |                                       |        |

|                  | $Q_t$ | $Q_{t+1}$ | J                                     | K      |

| J-K              | $Q_t$ | $Q_{t+1}$ | <i>J</i><br>0                         | K<br>d |

| J-K<br>flip-flop |       |           | , , , , , , , , , , , , , , , , , , , |        |

|                  | 0     | 0         | 0                                     | d<br>d |

|                  | 0     | 0         | 0<br>1                                | d<br>d |

| $Q_t$ | $Q_{t+1}$ | D |

|-------|-----------|---|

| 0     | 0         | 0 |

| 0     | 1         | 1 |

| 1     | 0         | 0 |

| 1     | 1         | 1 |

|                | $Q_t$  | $Q_{t+1}$   | Т     |

|----------------|--------|-------------|-------|

| T<br>flip-flop | 0 0 1  | 0<br>1<br>0 | 0 1 1 |

|                | 1<br>1 | 0           |       |

|                | 1      | 1           | 0     |

Principles of Computer Architecture by M. Murdocca and V. Heuring

© 1999 M. Murdocca and V. Heuring

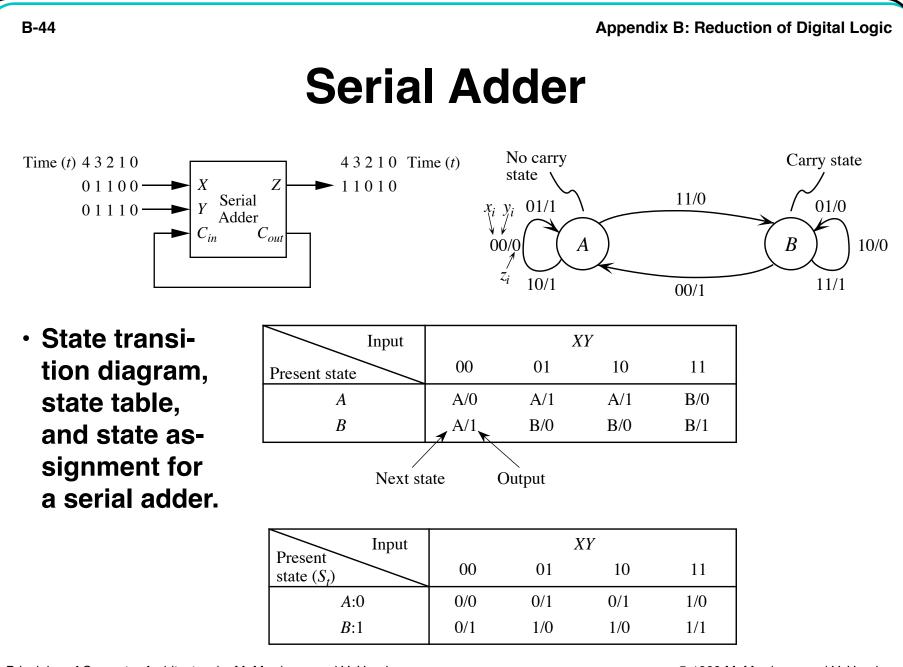

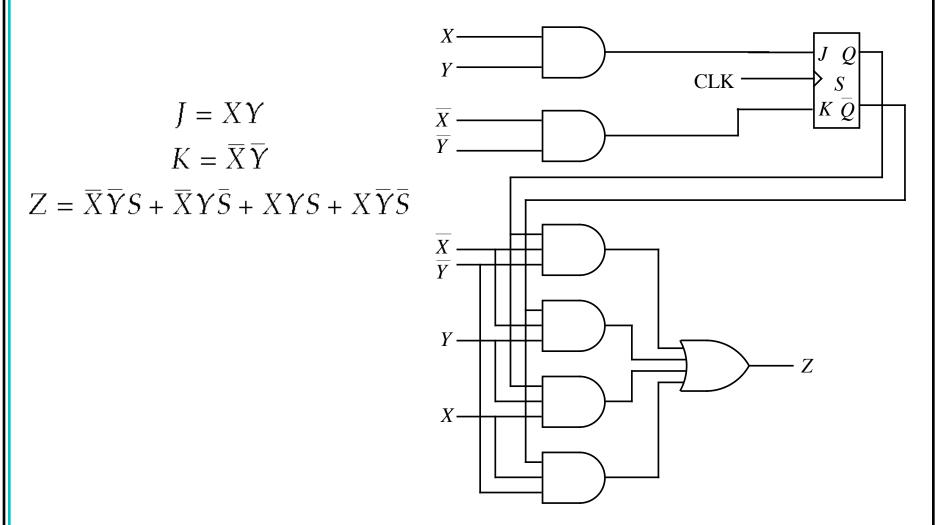

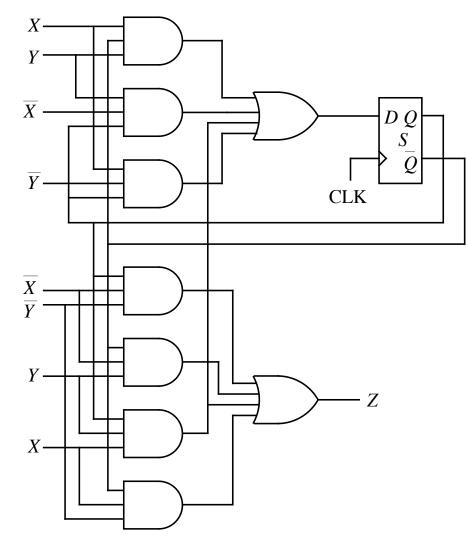

# **Serial Adder Next-State Functions**

Truth table showing next-state functions for a serial adder for D, S-R, T, and J-K flip-flops. Shaded functions are used in the example.

|   |   | resent<br>State |   | (Set) | (Reset) | ) |   |   |   |

|---|---|-----------------|---|-------|---------|---|---|---|---|

| X |   | $S_t$           | D | S     | R       | Т | J | K | Ζ |

| 0 | 0 | 0               | 0 | 0     | 0       | 0 | 0 | d | 0 |

| 0 | 0 | 1               | 0 | 0     | 1       | 1 | d | 1 | 1 |

| 0 | 1 | 0               | 0 | 0     | 0       | 0 | 0 | d | 1 |

| 0 | 1 | 1               | 1 | 0     | 0       | 0 | d | 0 | 0 |

| 1 | 0 | 0               | 0 | 0     | 0       | 0 | 0 | d | 1 |

| 1 | 0 | 1               | 1 | 0     | 0       | 0 | d | 0 | 0 |

| 1 | 1 | 0               | 1 | 1     | 0       | 1 | 1 | d | 0 |

| 1 | 1 | 1               | 1 | 0     | 0       | 0 | d | 0 | 1 |

Principles of Computer Architecture by M. Murdocca and V. Heuring

**Appendix B: Reduction of Digital Logic**

# **J-K Flip-Flop Serial Adder Circuit**

Principles of Computer Architecture by M. Murdocca and V. Heuring

© 1999 M. Murdocca and V. Heuring

# **D Flip-Flop Serial Adder Circuit**

© 1999 M. Murdocca and V. Heuring

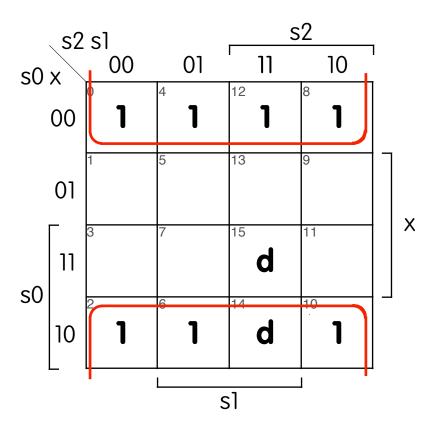

# CONSIDER FLIP FLOP CHOICE IN SEQUENCE DETECTOR (NOT COVERED)

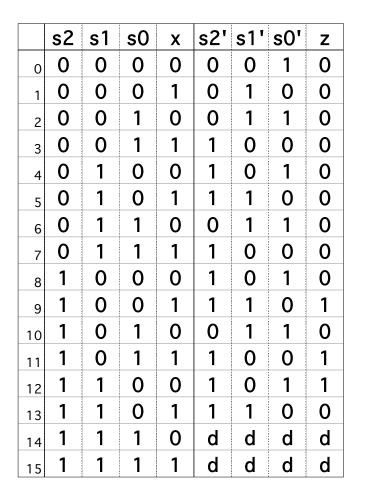

# **Sequence Detector State Assignment**

#### 7-state

#### new 6-state

|    | s2 | <b>s</b> 1 | s0 | X | s2' | s1' | s0' | Z | j2 | k2 | j1 | k1 | j0 | k0 |

|----|----|------------|----|---|-----|-----|-----|---|----|----|----|----|----|----|

| 0  | 0  | 0          | 0  | 0 | 0   | 0   | 1   | 0 | 0  | d  | 0  | d  | 1  | d  |

| 1  | 0  | 0          | 0  | 1 | 0   | 1   | 0   | 0 | 0  | d  | 1  | d  | 0  | d  |

| 2  | 0  | 0          | 1  | 0 | 0   | 0   | 1   | 0 | 0  | d  | 0  | d  | d  | 0  |

| 3  | 0  | 0          | 1  | 1 | 1   | 0   | 0   | 0 | 1  | d  | 0  | d  | d  | 1  |

| 4  | 0  | 1          | 0  | 0 | 1   | 0   | 1   | 0 | 1  | d  | d  | 1  | 1  | d  |

| 5  | 0  | 1          | 0  | 1 | 1   | 1   | 0   | 0 | 1  | d  | d  | 0  | 0  | d  |

| 6  | 0  | 1          | 1  | 0 | d   | d   | d   | d | d  | d  | d  | d  | d  | d  |

| 7  | 0  | 1          | 1  | 1 | d   | d   | d   | d | d  | d  | d  | d  | d  | d  |

| 8  | 1  | 0          | 0  | 0 | 1   | 0   | 1   | 0 | d  | 0  | 0  | d  | 1  | d  |

| 9  | 1  | 0          | 0  | 1 | 1   | 1   | 0   | 1 | d  | 0  | 1  | d  | 0  | d  |

| 10 | 1  | 0          | 1  | 0 | 0   | 0   | 1   | 0 | d  | 1  | 0  | d  | d  | 0  |

| 11 | 1  | 0          | 1  | 1 | 1   | 0   | 0   | 1 | d  | 0  | 0  | d  | d  | 1  |

| 12 | 1  | 1          | 0  | 0 | 1   | 0   | 1   | 1 | d  | 0  | d  | 1  | 1  | d  |

| 13 | 1  | 1          | 0  | 1 | 1   | 1   | 0   | 0 | d  | 0  | d  | 0  | 0  | d  |

| 14 | 1  | 1          | 1  | 0 | d   | d   | d   | d | d  | d  | d  | d  | d  | d  |

| 15 | 1  | 1          | 1  | 1 | d   | d   | d   | d | d  | d  | d  | d  | d  | d  |

**J2**

K2

01

d

d

d

d

12

13

15

sl

11

0

0

d

d

s2

10

0

0

0

٦

11

Х

J2 = s1 + s0 x

K2 = s0 x

s2 s1

s0 x

00

01

11

10

s0

00

d

d

d

d

**K1**

$J1 = \overline{s0} x$

K1 = x

JO

К0

$J0 = \overline{x}$

K0 = x

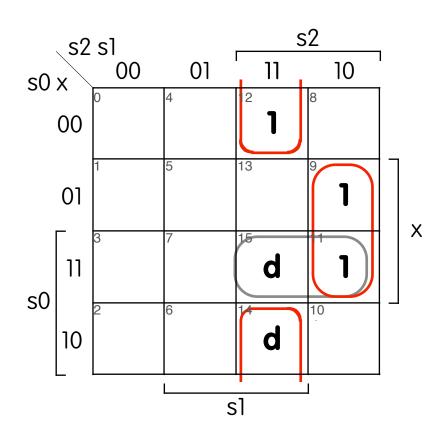

### **Improved Sequence Detector**

#### • Formulas for the 6-state FSM with D Flip-flops:

$$s2' = (\overline{s0} + x)(s2 + s1 + s0)$$

$$s1' = \overline{s0} x$$

$$s0' = \overline{x}$$

#### • Formulas for the 6-state FSM with J-K Flip-flops:

| J2 = | s1 + s0 x             | K2 = s0 x           |

|------|-----------------------|---------------------|

| J1 = | $=$ $\overline{s0}$ x | $K1 = \overline{x}$ |

| J0 = | —<br>×                | K0 = x              |

# **NEXT TIME**

• A 2-bit CPU