# CMSC 313 COMPUTER ORGANIZATION & ASSEMBLY LANGUAGE PROGRAMMING

LECTURE 25, FALL 2012

### **TOPICS TODAY**

- Finite State Machine Simplification

- A 2-bit "CPU"

# FINITE STATE MACHINE SIMPLIFICATION STEPS

- Minimize combinational logic circuit (hard)

- Reduce number of states

- Apply state assignment heuristics

- Consider choice of flip flops (e.g., J-K vs D)

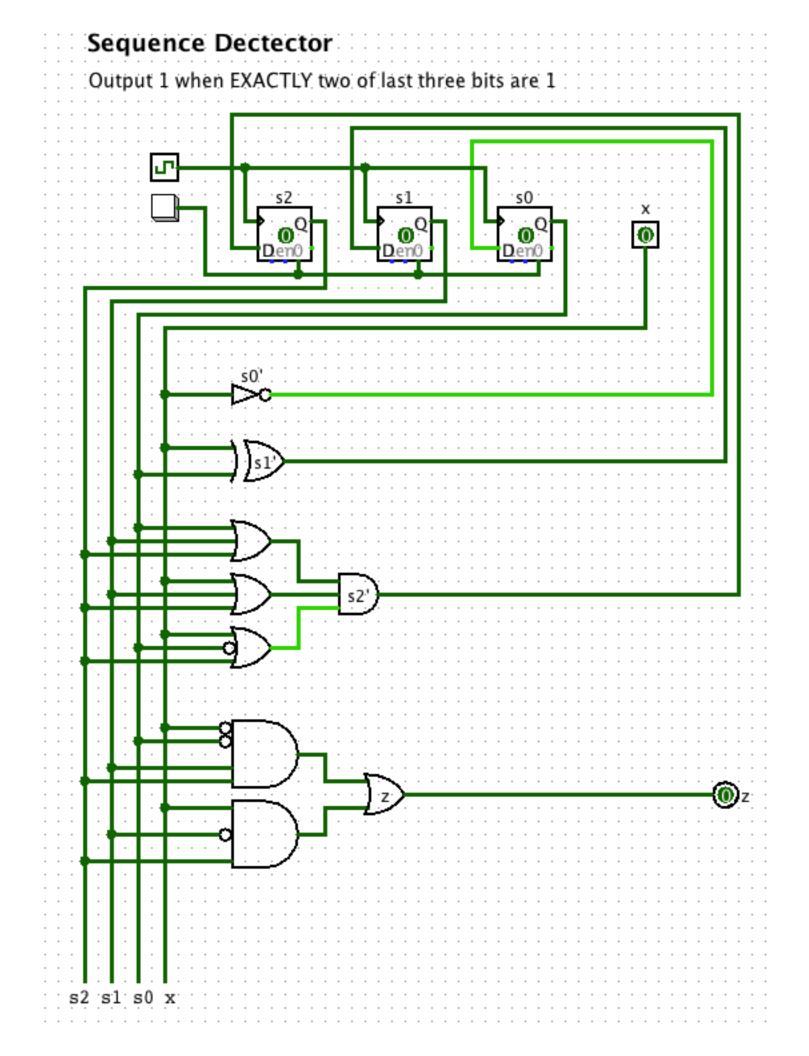

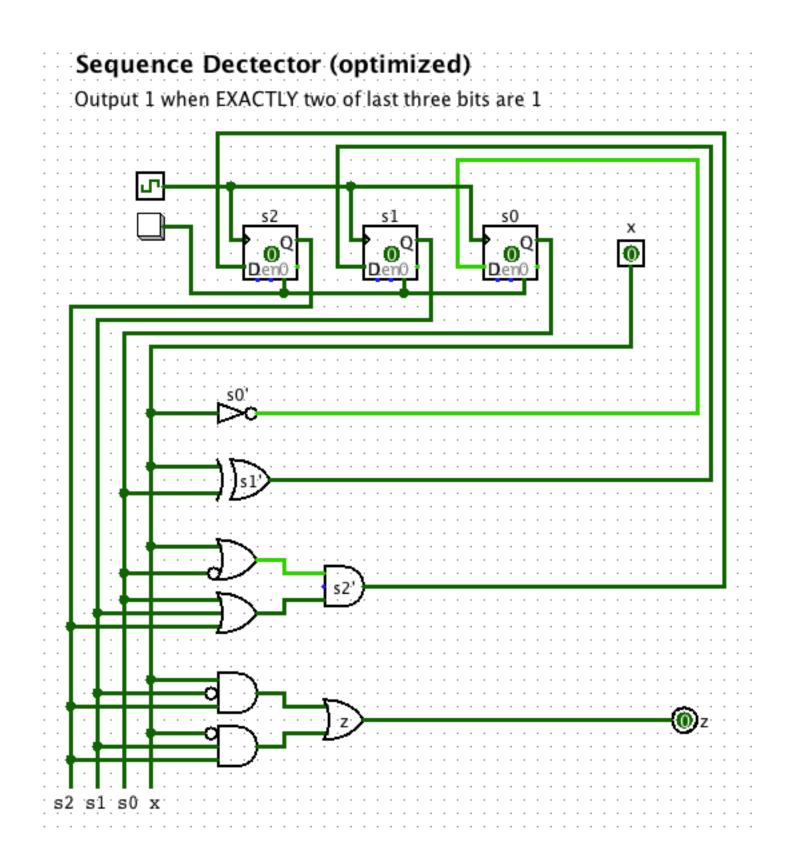

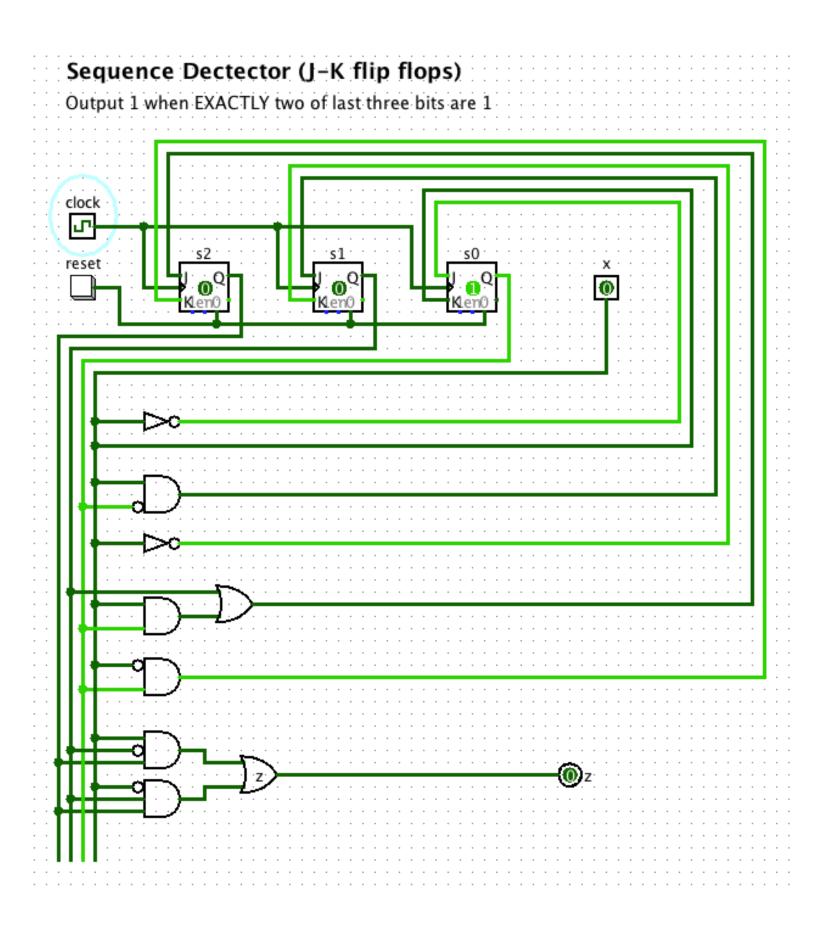

# EXAMPLE: SEQUENCE DETECTOR

# **Example: A Sequence Detector**

- <u>Example</u>: Design a machine that outputs a 1 when exactly two of the last three inputs are 1.

- e.g. input sequence of 011011100 produces an output sequence of 001111010.

- Assume input is a 1-bit serial line.

- Use D flip-flops and 8-to-1 Multiplexers.

- Start by constructing a state transition diagram (next slide).

Principles of Computer Architecture by M. Murdocca and V. Heuring

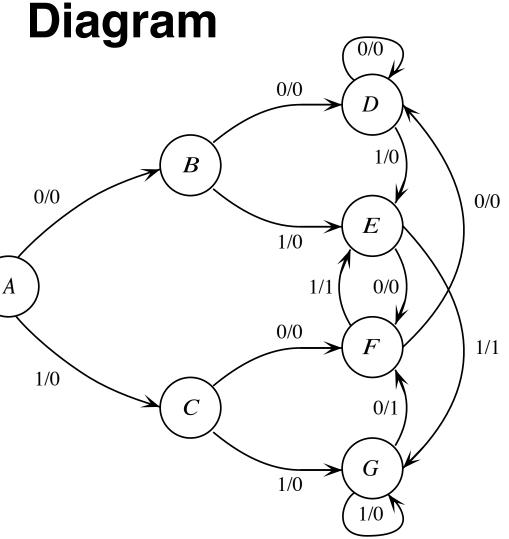

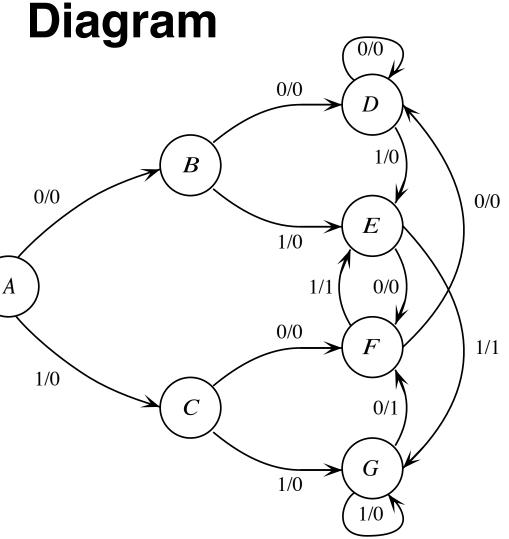

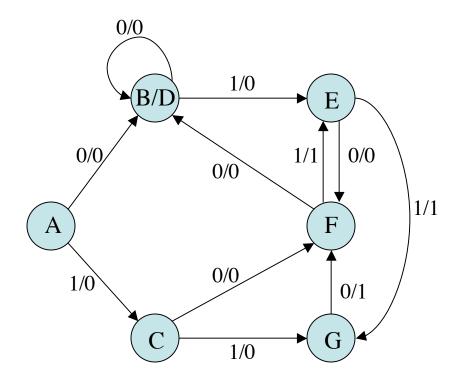

### Sequence Detector State Transition Diagram

Design a machine that outputs a 1 when exactly two of the last three inputs are 1.

Principles of Computer Architecture by M. Murdocca and V. Heuring

© 1999 M. Murdocca and V. Heuring

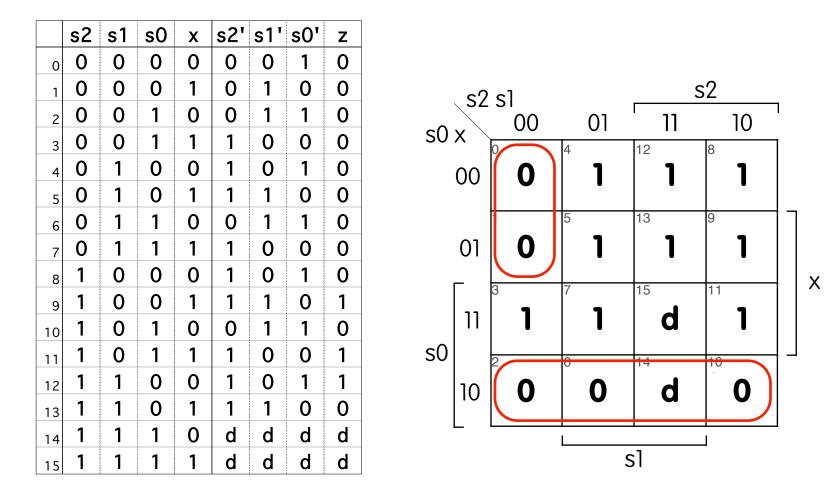

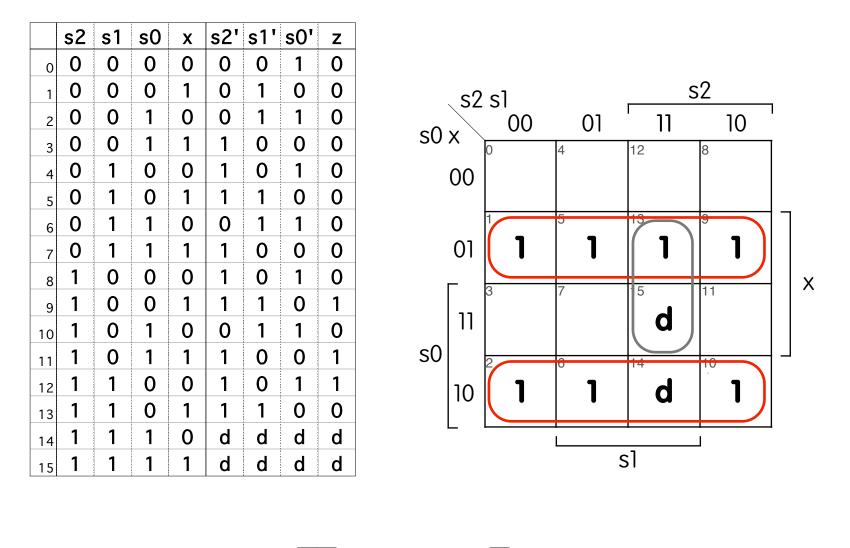

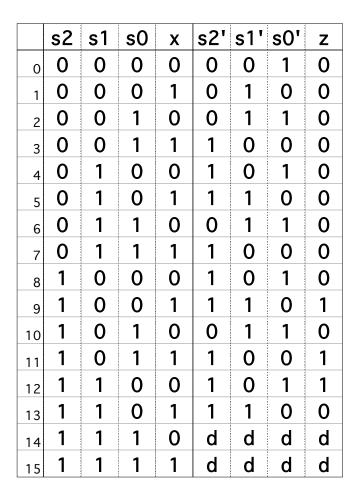

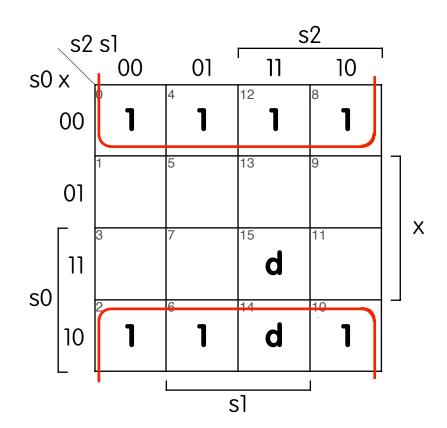

# COMBINATIONAL LOGIC CIRCUIT MINIMIZATION

$s2' = (\overline{s0} + x)(s2 + s1 + s0)$

$s1' = \overline{s0} x + s0 \overline{x} = s0 x r x$

$$s0' = \overline{x}$$

$$z = s2 \overline{s1} x + s2 s1 \overline{x}$$

# **Circuit Minimization is Hard**

#### • Unix systems store passwords in encrypted form.

$_{\odot}$  User types in x, system computes f(x) and looks for f(x) in a file.

Suppose we us 64-bit passwords and I want to find the password x, such that f(x) = y. Let

$g_i(x) = 0$  if f(x) = y and the ith bit of x is 0 1 otherwise.

- If the ith bit of x is 1, then g<sub>i</sub>(x) outputs 1 for every x and has a very, very simple circuit.

- If you can simplify every circuit quickly, then you can crack passwords quickly.

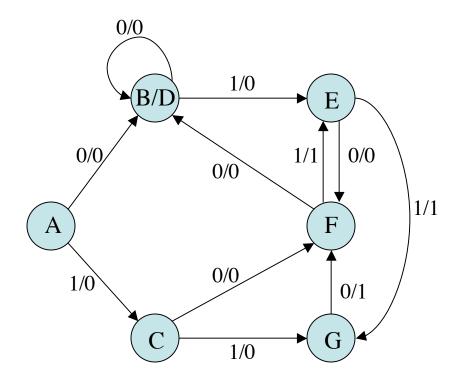

# **STATE REDUCTION**

### Sequence Detector State Transition Diagram

Design a machine that outputs a 1 when exactly two of the last three inputs are 1.

Principles of Computer Architecture by M. Murdocca and V. Heuring

© 1999 M. Murdocca and V. Heuring

**6-State Sequence Detector**

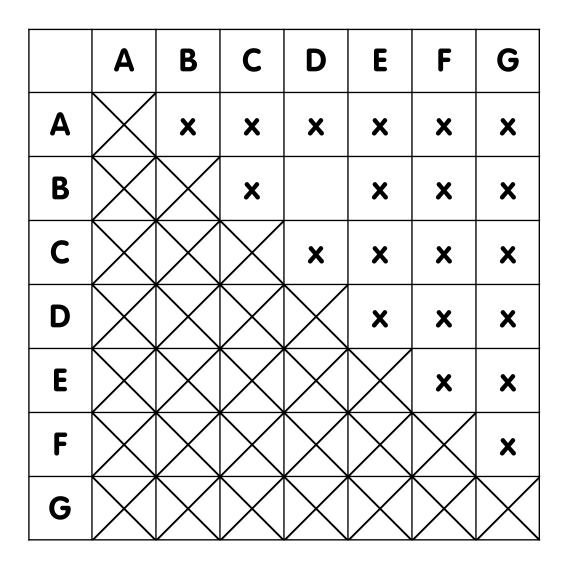

# **State Reduction Algorithm**

1. Use a 2-dimensional table — an entry for each pair of states.

2. Two states are "distinguished" if:

a. States X and Y of a finite state machine M are distinguished if there exists an input r such that the output of M in state X reading input r is different from the output of M in state Y reading input r.

b. States X and Y of a finite state machine are distinguished if there exists an input r such that M in state X reading input r goes to state X', M in state Y reading input r goes to state Y' and we already know that X' and Y' are distinguished states.

- 3. For each pair (X,Y), check if X and Y are distinguished using the definition above.

- 4. At the end of the algorithm, states that are not found to be distinguished are in fact equivalent.

### **Sequence Detector State Reduction Table**

# **State Reduction Algorithm Performance**

- As stated, the algorithm takes O(n<sup>4</sup>) time for a FSM with n states, because each pass takes O(n<sup>2</sup>) time and we make at most O(n<sup>2</sup>) passes.

- A more clever implementation takes O(n<sup>2</sup>) time.

- The algorithm produces a FSM with the fewest number states possible.

- Performance and correctness can be proven.

# **STATE ASSIGNMENT**

# **State Assignment Heuristics**

### • No known efficient alg. for best state assignment

### • Some heuristics (rules of thumb):

- $\diamond$  The initial state should be simple to reset all zeroes or all ones.

- Minimize the number of state variables that change on each transition.

- Maximize the number of state variables that don't change on each transition.

- Second Second

- If there are unused states (when the number of states s is not a power of 2), choose the unused state variable combinations carefully. (Don't just use the first s combination of state variables.)

- Decompose the set of state variables into bits or fields that have well-defined meaning with respect to the input or output behavior.

- Consider using more than the minimum number of states to achieve the objectives above.

**6-State Sequence Detector**

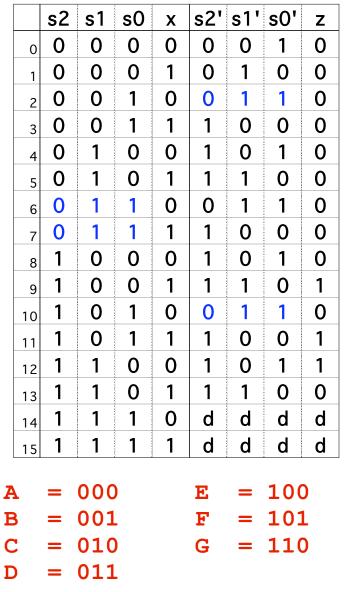

### **Sequence Detector State Assignment**

| X                         |

|---------------------------|

| 0 1                       |

| $S_2S_1S_0Z$ $S_2S_1S_0Z$ |

| 001/0 010/0               |

| 001/0 011/0               |

| 100/0 101/0               |

| 100/0 101/1               |

| 001/0 011/1               |

| 100/1 101/0               |

|                           |

Principles of Computer Architecture by M. Murdocca and V. Heuring

### **Improved Sequence Detector?**

#### • Formulas from the 7-state FSM:

$$s2' = (\overline{s0} + x) (s2 + s1 + s0)$$

$$s1' = \overline{s0} x + s0 \overline{x} = s0 \text{ xor } x$$

$$s0' = \overline{x}$$

$$z = s2 \overline{s1} x + s2 \overline{s1} \overline{x}$$

#### • Formulas from the 6-state FSM:

$$s2' = s2 s0 + s1$$

$$s1' = \overline{s2} \overline{s1} x + s2 \overline{s0} x$$

$$s0' = \overline{s2} \overline{s1} \overline{x} + s0 x + s2 \overline{s0} + s1 x$$

$$z = s2 \overline{s0} x + s1 s0 x + s2 s0 \overline{x}$$

UMBC, CMSC313, Richard Chang <chang@umbc.edu>

### **Sequence Detector State Assignment**

#### 7-state

#### new 6-state

UMBC, CMSC313, Richard Chang <chang@umbc.edu>

### **Improved Sequence Detector**

#### • Textbook formulas for the 6-state FSM:

$$s2' = s2 s0 + s1$$

$$s1' = \overline{s2} \overline{s1} x + s2 \overline{s0} x$$

$$s0' = \overline{s2} \overline{s1} \overline{x} + s0 x + s2 \overline{s0} + s1 x$$

$$z = s2 \overline{s0} x + s1 s0 x + s2 s0 \overline{x}$$

#### • New formulas for the 6-state FSM:

$$s2' = (\overline{s0} + x) (s2 + s1 + s0)$$

$$s1' = \overline{s0} x$$

$$s0' = \overline{x}$$

$$z = s2 \overline{s1} x + s2 \overline{s1} \overline{x}$$

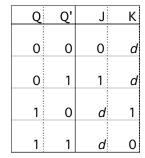

# **CHOICE OF FLIP FLOP**

D

flip-flop

### **Excitation Tables**

• Each table shows the settings that must be applied at the inputs at time t in order to change the outputs at time *t*+1.

|                  | $Q_t$ | $Q_{t+1}$ | S                                     | R      |

|------------------|-------|-----------|---------------------------------------|--------|

| S-R              | 0     | 0         | 0                                     | 0      |

| flip-flop        | 0     | 1         | 1                                     | 0      |

|                  | 1     | 0         | 0                                     | 1      |

|                  | 1     | 1         | 0                                     | 0      |

|                  |       |           |                                       |        |

|                  | $Q_t$ | $Q_{t+1}$ | J                                     | K      |

| J-K              | $Q_t$ | $Q_{t+1}$ | <i>J</i><br>0                         | K<br>d |

| J-K<br>flip-flop |       |           | , , , , , , , , , , , , , , , , , , , |        |

|                  | 0     | 0         | 0                                     | d<br>d |

|                  | 0     | 0         | 0<br>1                                | d<br>d |

| $Q_t$ | $Q_{t+1}$ | D |

|-------|-----------|---|

| 0     | 0         | 0 |

| 0     | 1         | 1 |

| 1     | 0         | 0 |

| 1     | 1         | 1 |

|                | $Q_t$  | $Q_{t+1}$   | Т     |

|----------------|--------|-------------|-------|

| T<br>flip-flop | 0 0 1  | 0<br>1<br>0 | 0 1 1 |

|                | 1<br>1 | 0           |       |

|                | 1      | 1           | 0     |

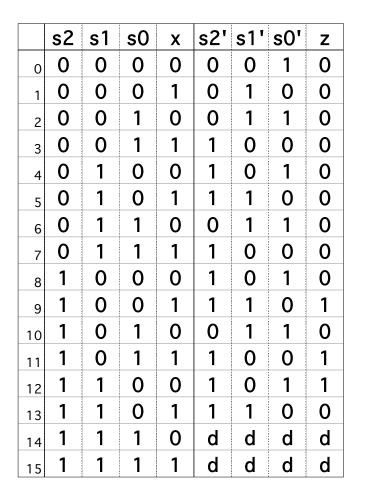

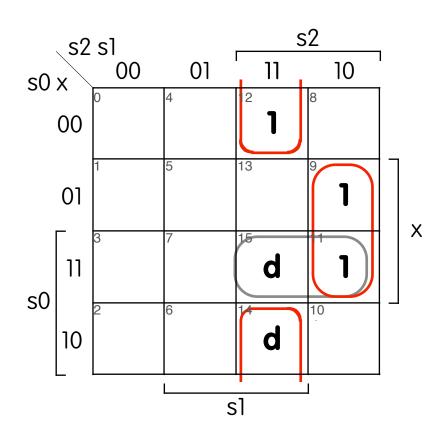

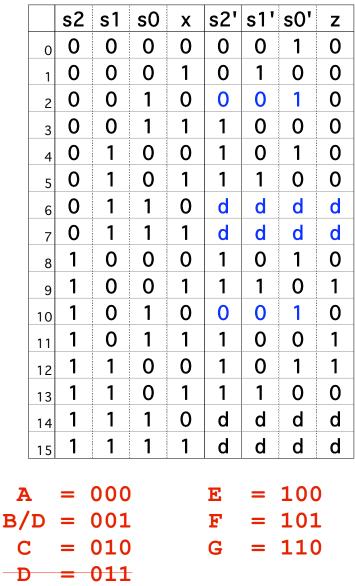

### **6-State Sequence Detector**

|    | s2 | <b>s</b> 1 | s0 | X | s2' | s1' | s0' | Z | j2 | k2 | j1 | k1 | j0 | k0 |

|----|----|------------|----|---|-----|-----|-----|---|----|----|----|----|----|----|

| 0  | 0  | 0          | 0  | 0 | 0   | 0   | 1   | 0 | 0  | d  | 0  | d  | 1  | d  |

| 1  | 0  | 0          | 0  | 1 | 0   | 1   | 0   | 0 | 0  | d  | 1  | d  | 0  | d  |

| 2  | 0  | 0          | 1  | 0 | 0   | 0   | 1   | 0 | 0  | d  | 0  | d  | d  | 0  |

| 3  | 0  | 0          | 1  | 1 | 1   | 0   | 0   | 0 | 1  | d  | 0  | d  | d  | 1  |

| 4  | 0  | 1          | 0  | 0 | 1   | 0   | 1   | 0 | 1  | d  | d  | 1  | 1  | d  |

| 5  | 0  | 1          | 0  | 1 | 1   | 1   | 0   | 0 | 1  | d  | d  | 0  | 0  | d  |

| 6  | 0  | 1          | 1  | 0 | d   | d   | d   | d | d  | d  | d  | d  | d  | d  |

| 7  | 0  | 1          | 1  | 1 | d   | d   | d   | d | d  | d  | d  | d  | d  | d  |

| 8  | 1  | 0          | 0  | 0 | 1   | 0   | 1   | 0 | d  | 0  | 0  | d  | 1  | d  |

| 9  | 1  | 0          | 0  | 1 | 1   | 1   | 0   | 1 | d  | 0  | 1  | d  | 0  | d  |

| 10 | 1  | 0          | 1  | 0 | 0   | 0   | 1   | 0 | d  | 1  | 0  | d  | d  | 0  |

| 11 | 1  | 0          | 1  | 1 | 1   | 0   | 0   | 1 | d  | 0  | 0  | d  | d  | 1  |

| 12 | 1  | 1          | 0  | 0 | 1   | 0   | 1   | 1 | d  | 0  | d  | 1  | 1  | d  |

| 13 | 1  | 1          | 0  | 1 | 1   | 1   | 0   | 0 | d  | 0  | d  | 0  | 0  | d  |

| 14 | 1  | 1          | 1  | 0 | d   | d   | d   | d | d  | d  | d  | d  | d  | d  |

| 15 | 1  | 1          | 1  | 1 | d   | d   | d   | d | d  | d  | d  | d  | d  | d  |

### **Improved Sequence Detector**

#### • Formulas for the 6-state FSM with D Flip-flops:

$$s2' = (\overline{s0} + x)(s2 + s1 + s0)$$

$$s1' = \overline{s0} x$$

$$s0' = \overline{x}$$

#### • Formulas for the 6-state FSM with J-K Flip-flops:

| J2 = | s1 + s0 x             | K2 = s0 x           |

|------|-----------------------|---------------------|

| J1 = | $=$ $\overline{s0}$ x | $K1 = \overline{x}$ |

| J0 = | —<br>×                | K0 = x              |

UMBC, CMSC313, Richard Chang <chang@umbc.edu>

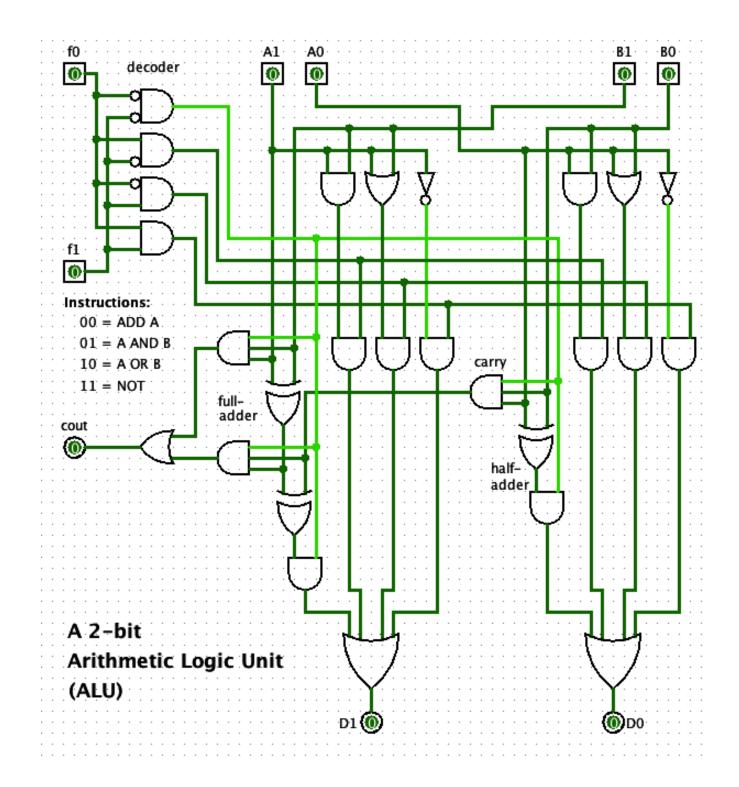

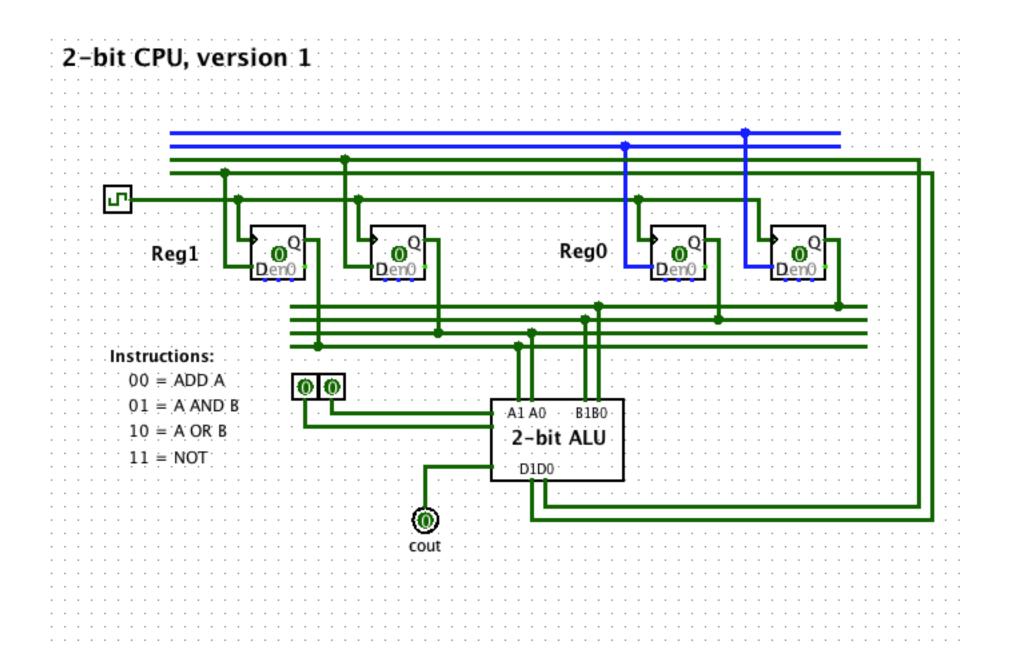

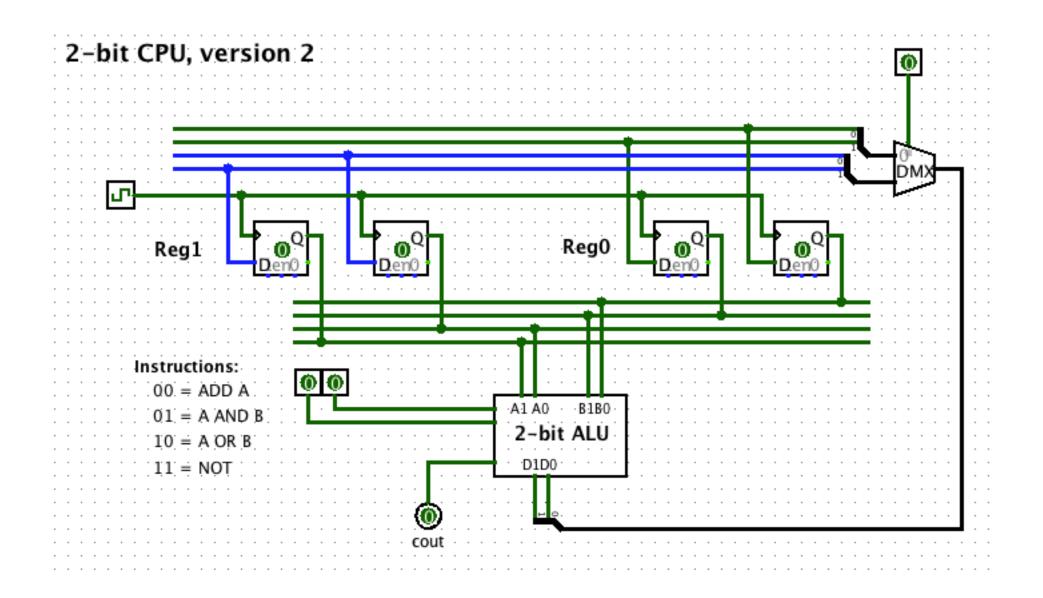

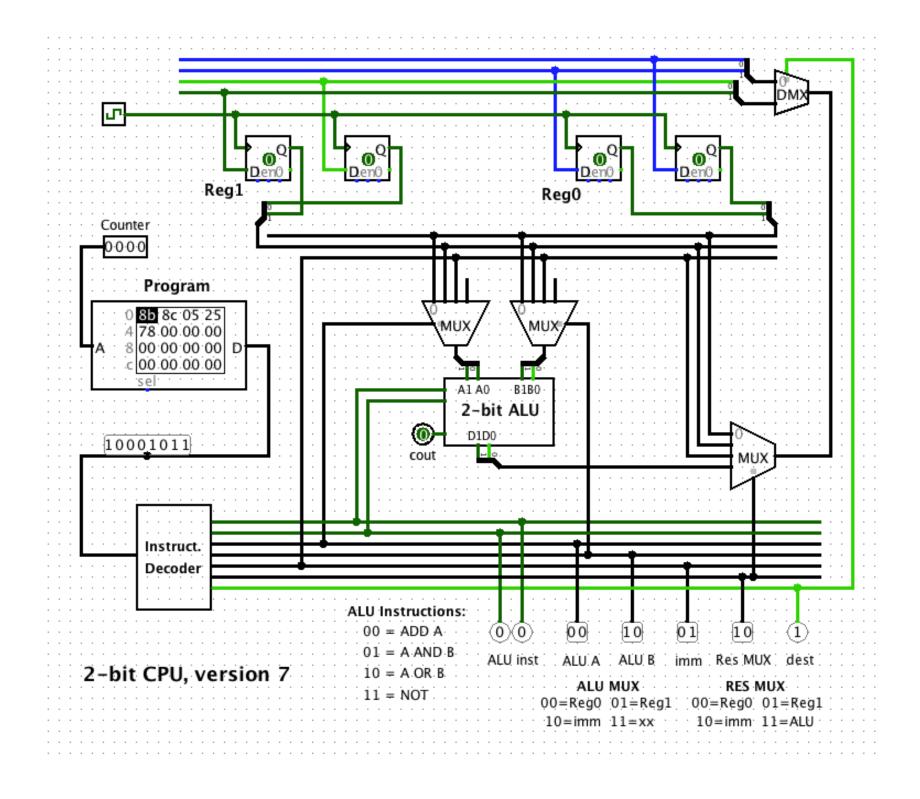

# A 2-BIT "CPU"

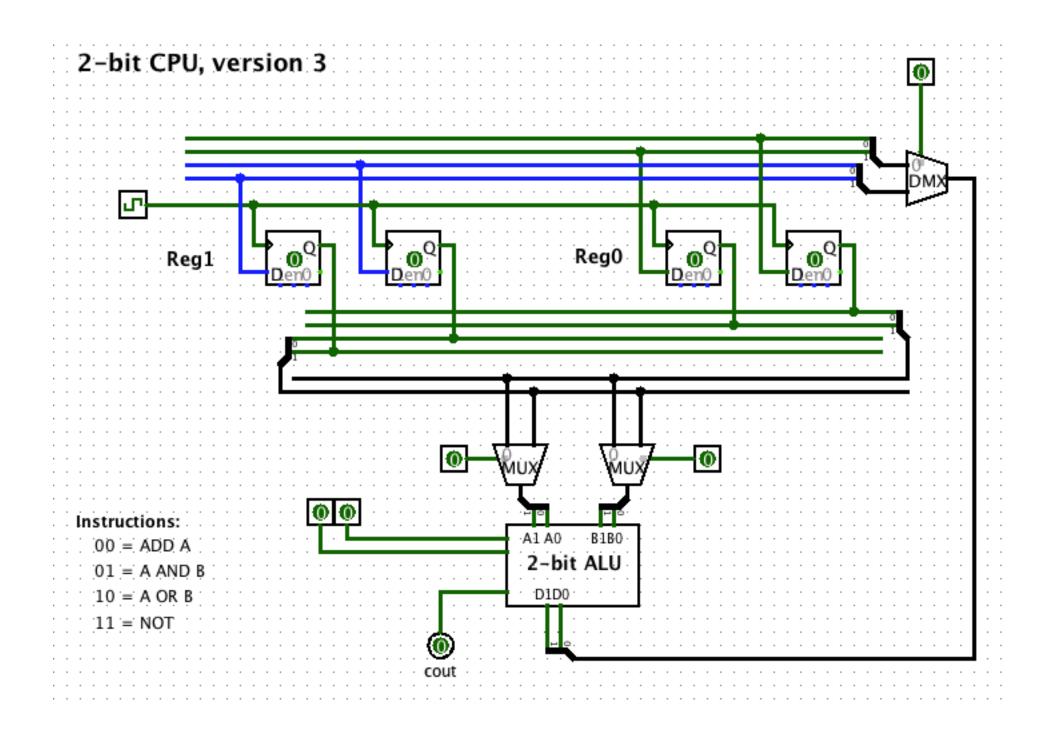

# **2-BIT CPU: VERSION 1**

- 2-bit ALU in sub-circuit

- Connect two 2-bit registers to 2-bit ALU

- Output of ALU stored in Register 1

- Use DEMUX to select destination register

- Use Logisim wire bundles

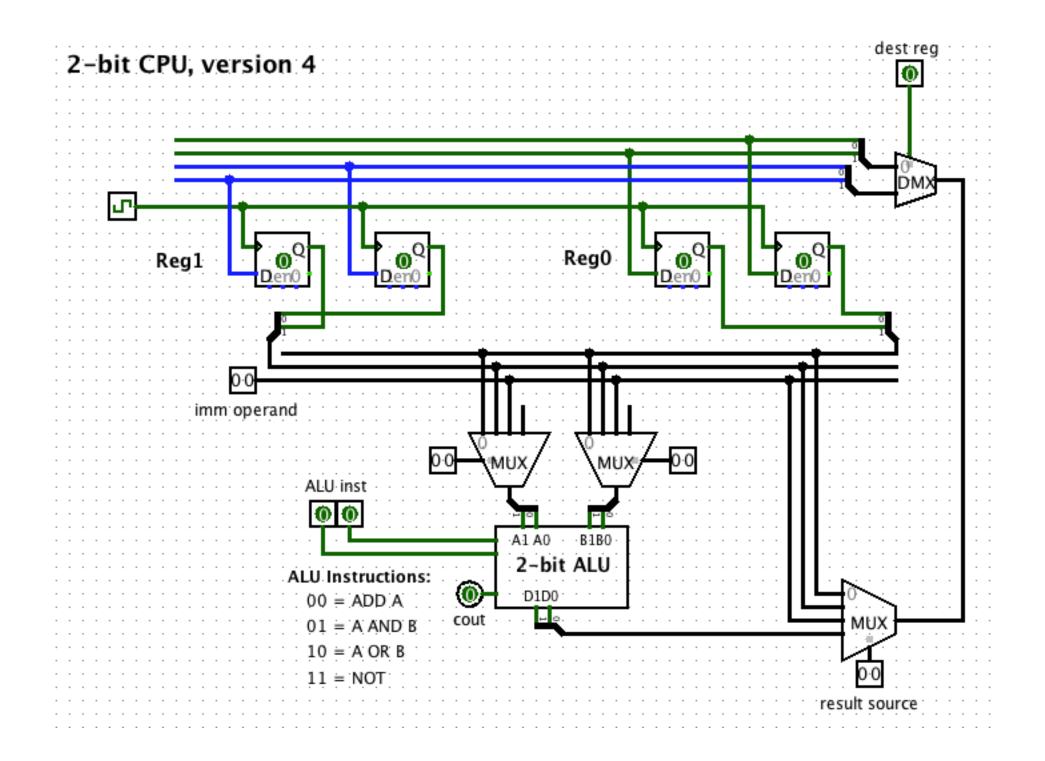

Use MUX to select input to each ALU "port".

- Simplify "data bus" using wire bundles

- Add immediate operand to data bus

- Use result MUX to select input to DEMUX for destination register. Input may be:

- Register 0

- Register 1

- Immediate Operand

- ALU output

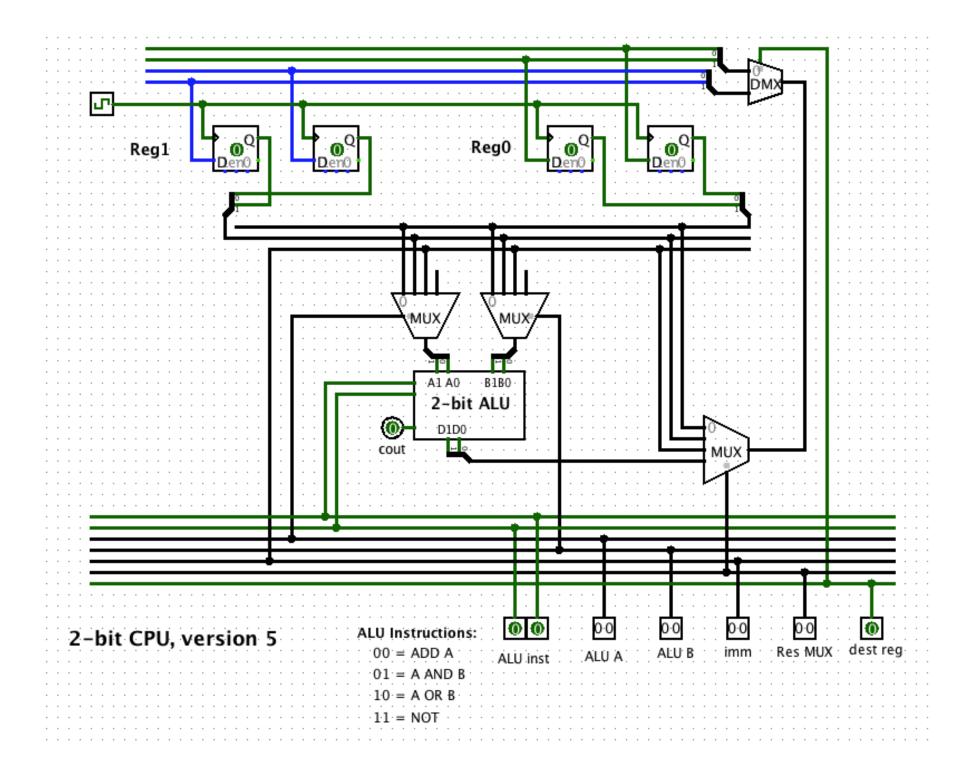

Consolidate controls to a "control bus"

#### **Use 8-bit "instruction code"**

| i7 | i6 | i5 | i4 | i3 | i2 | i1 | i0 |

|----|----|----|----|----|----|----|----|

| 0  |    |    |    |    |    |    |    |

- i7: 0 if ALU instruction, 1 otherwise

- i6 i5: ALU instruction

- i4: operand 1 register (Reg 0 or Reg 1)

- i3 i2 i1: 0rx = operand 2 is Reg r 1xy = immediate operand xy

- i0: destination register

#### **Use 8-bit "instruction code"**

| i7 | i6 | i5 | i4 | i3 | i2 | i1 | iO |

|----|----|----|----|----|----|----|----|

| 1  | 0  | 0  | 0  |    |    |    |    |

i7: 0 if ALU instruction, 1 otherwise

i6 i5 i4: 000 = move, others not implemented

i3 i2 i1: 0rx = source operand is Reg r 1xy = immediate operand xy

i0: destination register

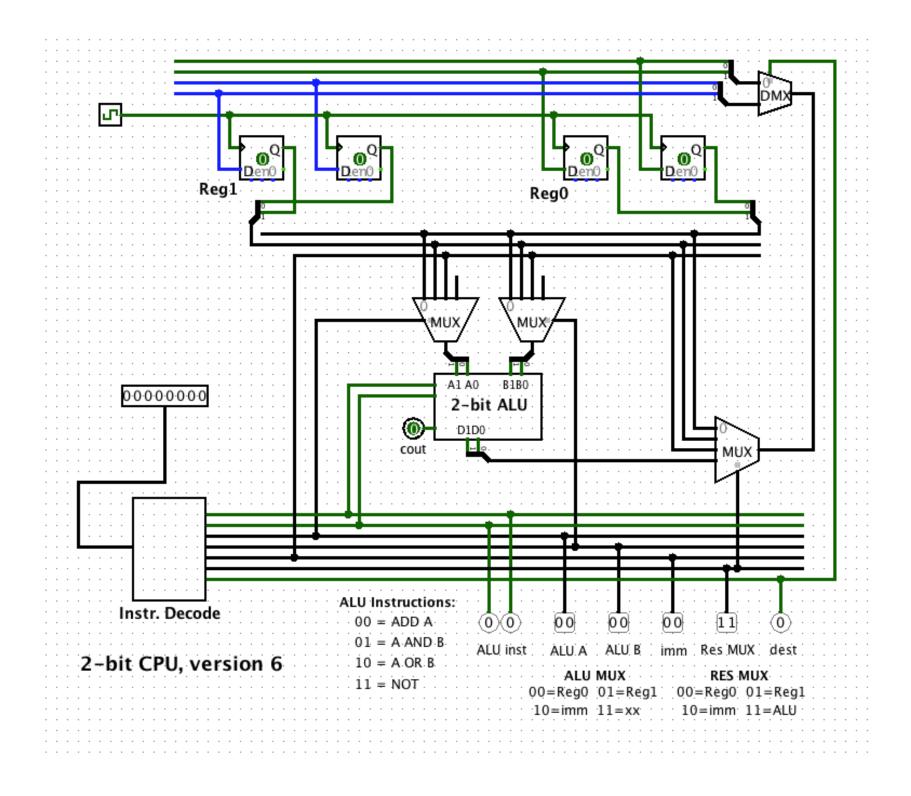

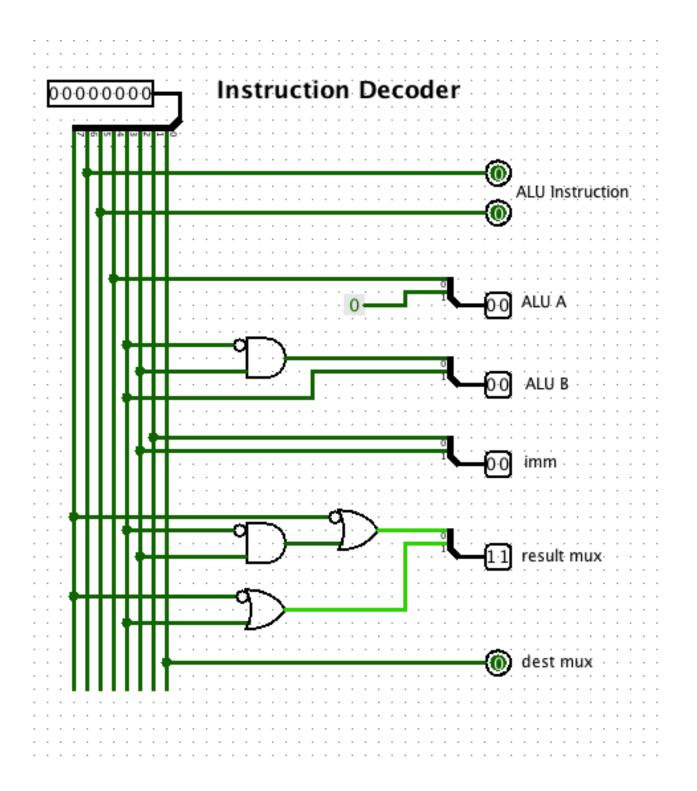

### **INSTRUCTION DECODER**

| MUX for ALU port B                                          | i3                                                                                                                                                                                                                                                 | i2 | i1 | В1 | в0 |         |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|----|----|----|---------|

|                                                             | 0                                                                                                                                                                                                                                                  | 0  | 0  | 0  | 0  |         |

| B1 = i3                                                     | 0                                                                                                                                                                                                                                                  | 0  | 1  | 0  | 0  | F Reg U |

|                                                             | 0                                                                                                                                                                                                                                                  | 1  | 0  | 0  | 1  |         |

| $B0 = \overline{i3} i2 \overline{i1} + \overline{i3} i2 i1$ | 0                                                                                                                                                                                                                                                  | 1  | 1  | 0  | 1  | F Reg 1 |

| $=$ $\overline{i3}$ $i2$                                    | 1                                                                                                                                                                                                                                                  | 0  | 0  | 1  | 0  | ]       |

|                                                             | $   \begin{bmatrix}     0 & 0 & 0 & 0 & 0 \\     0 & 0 & 1 & 0 & 0 \\     0 & 1 & 0 & 0 & 1 \\     0 & 1 & 1 & 0 & 1 \\     1 & 0 & 0 & 1 & 0 \\     1 & 0 & 1 & 1 & 0 \\     1 & 1 & 0 & 1 & 0 \\     1 & 1 & 0 & 1 & 0   \end{bmatrix}   Reg 1 $ |    |    |    |    |         |

|                                                             | 1                                                                                                                                                                                                                                                  | 1  | 0  | 1  | 0  |         |

|                                                             | 1                                                                                                                                                                                                                                                  | 1  | 1  | 1  | 0  |         |

### **INSTRUCTION DECODER**

| Res | Result MUX control |           |   |    |    |  |  |  |  |  |  |

|-----|--------------------|-----------|---|----|----|--|--|--|--|--|--|

| M1  | =                  | <u>i7</u> | + | i3 |    |  |  |  |  |  |  |

| М0  | =                  | <u>i7</u> | + | i3 | i2 |  |  |  |  |  |  |

| i7 | i3 | i2 | i1 | M1 | м0 |        |

|----|----|----|----|----|----|--------|

| 0  | 0  | 0  | 0  | 1  | 1  | ן      |

| 0  | 0  | 0  | 1  | 1  | 1  |        |

| 0  | 0  | 1  | 0  | 1  | 1  |        |

| 0  | 0  | 1  | 1  | 1  | 1  | - ALU  |

| 0  | 1  | 0  | 0  | 1  | 1  |        |

| 0  | 1  | 0  | 1  | 1  | 1  |        |

| 0  | 1  | 1  | 0  | 1  | 1  |        |

| 0  | 1  | 1  | 1  | 1  | 1  |        |

| 1  | 0  | 0  | 0  | 0  | 0  | Reg0   |

| 1  | 0  | 0  | 1  | 0  | 0  | , Regu |

| 1  | 0  | 1  | 0  | 0  | 1  |        |

| 1  | 0  | 1  | 1  | 0  | 1  | Reg1   |

| 1  | 1  | 0  | 0  | 1  | 0  | ]      |

| 1  | 1  | 0  | 1  | 1  | 0  | - Imm  |

| 1  | 1  | 1  | 0  | 1  | 0  |        |

| 1  | 1  | 1  | 1  | 1  | 0  |        |

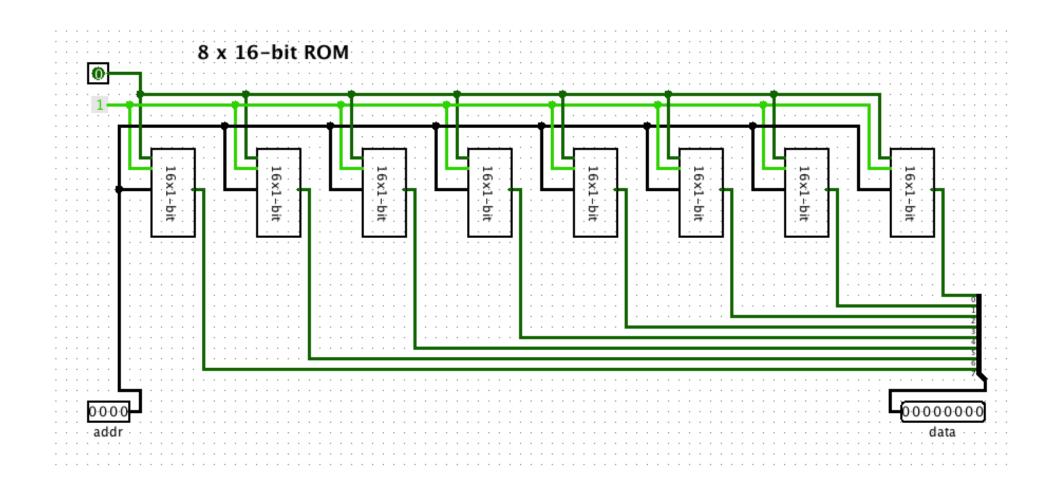

Added Program ROM which can store up to 16 instructions.

| •   | 00          |         |        |        | 📄 as    | ssembler.x | dsx    |          |      |     |     | Ma |

|-----|-------------|---------|--------|--------|---------|------------|--------|----------|------|-----|-----|----|

| 1   | Home        | Layout  | Tables | Charts | SmartAr | t Form     | ulas D | ata Re   | view |     | V 1 | ¢  |

|     | P19         | ÷ 😣     |        |        |         |            |        |          |      |     |     | -  |

|     | ~           | В       | С      | D      | E       | F          | G      | Н        | 1    | J   | K   |    |

| 1   | Instruction | op1     | op2    | result | i7      | i6 i5      | i4     | i3 i2 i1 | iO   | DEC | HEX | 41 |

| 2   | MOV         |         | 1      | R1     | 1       | 0          | 0      | 5        | 1    | 139 | 8B  |    |

| 3   | MOV         |         | 2      | RO     | 1       | 0          | 0      | 6        | 0    | 140 | 8C  |    |

| 4   | ADD         | RO      | R1     | R1     | 0       | 0          | 0      | 2        | 1    | 5   | 5   |    |

| 5   | AND         | RO      | R1     | R1     | 0       | 1          | 0      | 2        | 1    | 37  | 25  |    |

| 6   | NOT         | R1      |        | RO     | 0       | 3          | 1      | 4        | 0    | 120 | 78  |    |

| 7   | ADD         | RO      | RO     | RO     | 0       | 0          | 0      | 0        | 0    | 0   | 0   |    |

| 8   | ADD         | RO      | RO     | RO     | 0       | 0          | 0      | 0        | 0    | 0   | 0   |    |

| 9   | ADD         | RO      | RO     | RO     | 0       | 0          | 0      | 0        | 0    | 0   | 0   |    |

| 10  | ADD         | RO      | RO     | RO     | 0       | 0          | 0      | 0        | 0    | 0   | 0   |    |

| 11  | ADD         | RO      | RO     | RO     | 0       | 0          | 0      | 0        | 0    | 0   | 0   |    |

| 12  | ADD         | RO      | RO     | RO     | 0       | 0          | 0      | 0        | 0    | 0   | 0   | 1  |

| 13  | ADD         | RO      | RO     | RO     | 0       | 0          | 0      | 0        | 0    | 0   | 0   |    |

| 14  | ADD         | RO      | RO     | RO     | 0       | 0          | 0      | 0        | 0    | 0   | 0   |    |

| 15  | ADD         | RO      | RO     | RO     | 0       | 0          | 0      | 0        | 0    | 0   | 0   |    |

| 6   | ADD         | RO      | RO     | RO     | 0       | 0          | 0      | 0        | 0    | 0   | 0   | 1  |

| 17  | ADD         | RO      | RO     | RO     | 0       | 0          | 0      | 0        | 0    | 0   | 0   |    |

| 4 4 | S           | heet1 + |        |        |         |            |        |          |      | Y   |     |    |

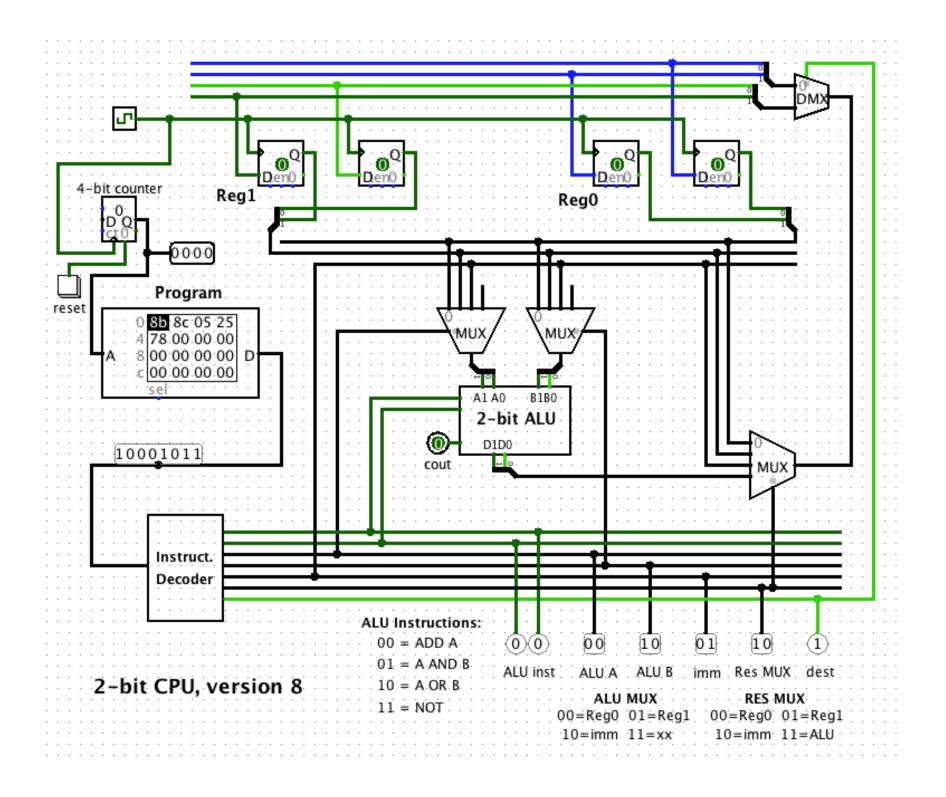

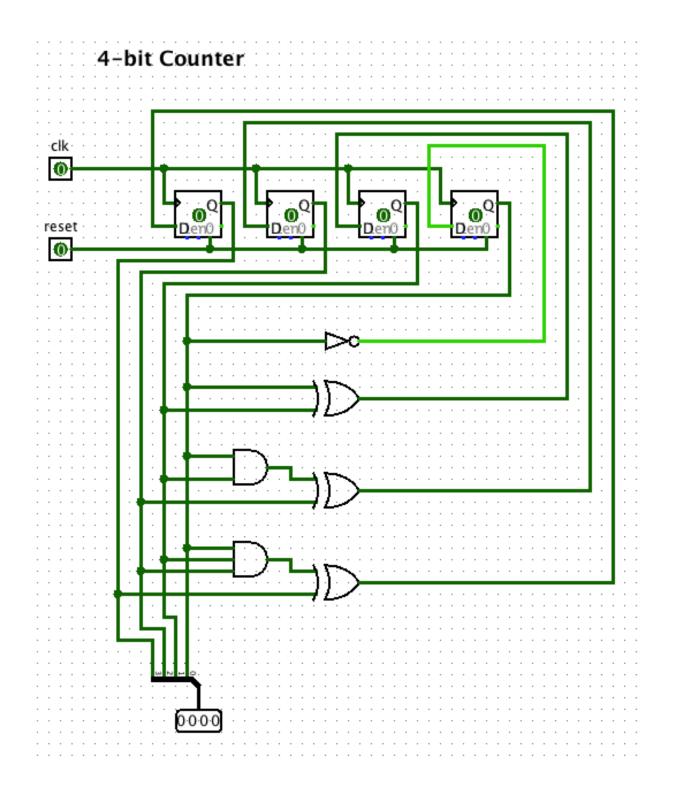

Added 4-bit counter which automatically advances Program ROM to next instruction.

Implement 4-bit counter from scratch.

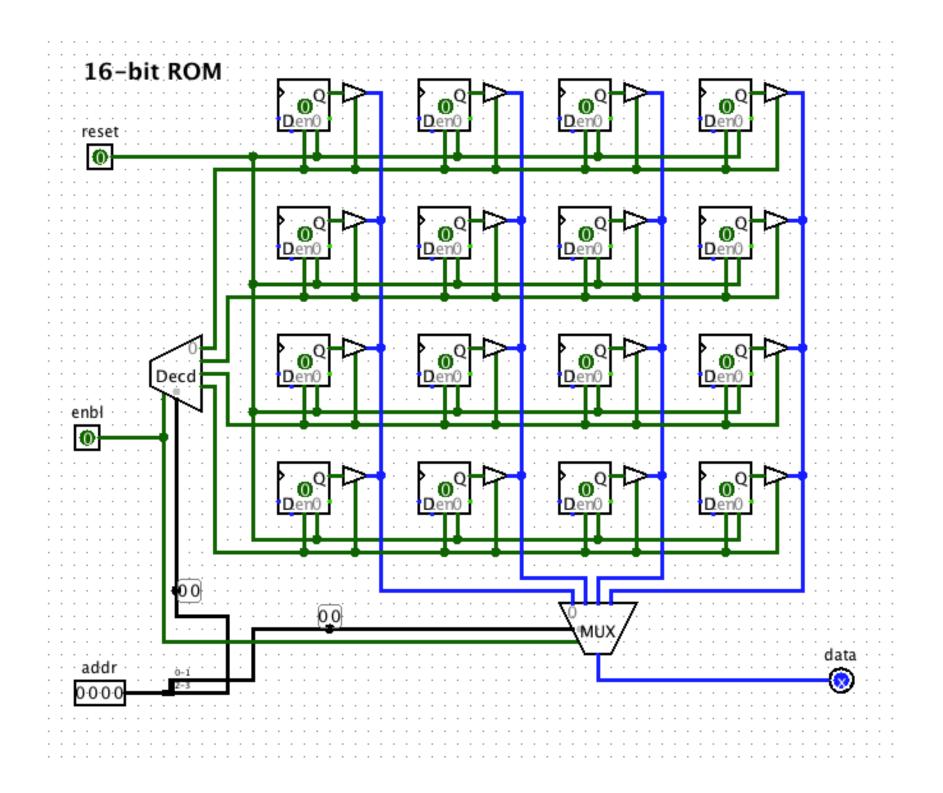

Implement Program ROM from scratch.

# NEXT TIME

- Memory Hierarchy

- Virtual Memory